**User's Manual**

# **V30MX**<sup>TM</sup>

**CPU CORE**

Document No. A11897EJ1V0UM00 (1st edition) Date Published April 1997 N

© NEC Corporation 1997 Printed in Japan [MEMO]

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

#### PREFACE

The V30MX is an ASIC original CPU core with bus efficiency improved by separating addresses from the data bus of the  $\mu$ PD70116H (V30HL<sup>TM</sup>), an NEC general-purpose microcomputer.

Since the V30MX has the same instruction set as that of the V30HL, existing programs can be used without changes.

Read this document thoroughly in order to carry out LSI design successfully. Be sure to observe the points that are described in the manual (general points, cautions and restrictions). Failing to observe them may cause deterioration of the quality and abnormalities in operation of the LSI product.

- **Readers** : This manual is intended for users who have an understanding of the V30MX functions and wish to design an application system using the V30MX functions.

- **Purpose** : This manual is intended to help users understand the V30MX hardware functions and has the following configuration.

Configuration: This V30MX User's Manual consists of a hardware volume (this manual) and an instruction volume.

|                       | This            | manual                                            |  | Instruction                                       |                                               |

|-----------------------|-----------------|---------------------------------------------------|--|---------------------------------------------------|-----------------------------------------------|

|                       | Pin funct       | ions                                              |  | Outline of instructions                           |                                               |

|                       | CPU fun         | ctions                                            |  | Description of instructio                         | ns                                            |

| Bus control functions |                 |                                                   |  |                                                   |                                               |

|                       | Interrupt       | functions                                         |  |                                                   |                                               |

|                       | Standby         | functions                                         |  |                                                   |                                               |

|                       | Reset functions |                                                   |  |                                                   |                                               |

|                       | Test func       | tions                                             |  |                                                   |                                               |

|                       |                 |                                                   |  |                                                   |                                               |

| How to Read thi       | s Manual:       | This manual assum and microcomputer               |  | /ou have a general underst                        | anding of electric circuits, logical circuits |

|                       |                 |                                                   |  | nding of the V30MX functio the table of contents. | ns                                            |

|                       |                 | To find details of ins $\rightarrow$ Refer to the |  |                                                   | <sup>M</sup> User's Manual – Instruction.     |

#### Legend:

| Active-low notation | : | $\times \times \times B$ (B at the end of pin name, signal name) |

|---------------------|---|------------------------------------------------------------------|

| Memory map address  | : | Upper side - higher address, lower side - lower address          |

| Note                | : | Explanation of item marked with "Note" in the text               |

| Caution             | : | Item to be especially noted                                      |

| Remark              | : | Supplementary information                                        |

| Numeric notations   | : | Binary xxx or xxxB<br>Decimal xxx<br>HexadecimalxxH              |

#### **Related documents:**

Note that the related documents may be preliminary versions, but there are not indicated as such in this document.

#### • User's Manual – Hardware

V30MX User's Manual : This document V20HL<sup>TM</sup>, V30HL, User's Manual – Hardware : IEM-1124A

#### • User's Manual - Instruction

16-Bit V Series User's Manual – Instruction : U11301E

When designing, contact your NEC sales representative or domestic sales agent to make sure you are using the latest documentations.

### TABLE OF CONTENTS

| CHAPTER | 1 G      |                                            | . 1 |

|---------|----------|--------------------------------------------|-----|

| 1.1     | Featur   | es                                         | . 1 |

| 1.2     | Outline  | of Differences from V30HL                  | . 1 |

| 1.3     | Symbo    | l Diagram                                  | . 2 |

| 1.4     | Interna  | I Block Diagram                            | . 3 |

| CHAPTER | 2 P      |                                            | . 5 |

| 2.1     | Pin Lis  | t                                          | . 5 |

| 2.2     | Descri   | ption of Pin Functions                     | . 6 |

| 2.3     | Pin Inf  | ormation in Specific Status                | 13  |

| CHAPTER | 3 C      | PU FUNCTIONS                               | 15  |

| 3.1     | Regist   | er Configuration                           | 15  |

|         | 3.1.1    | General-purpose registers (AW, BW, CW, DW) | 15  |

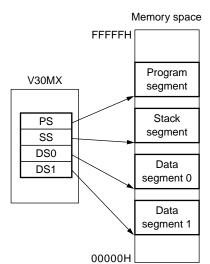

|         | 3.1.2    | Segment registers (PS, SS, DS0, DS1)       | 15  |

|         | 3.1.3    | Pointer (SP, BP)                           | 16  |

|         | 3.1.4    | Program counter (PC)                       | 16  |

|         | 3.1.5    | Program status word (PSW)                  | 16  |

|         | 3.1.6    | Index register (IX, IY)                    | 20  |

| 3.2     | Addres   | s Space                                    | 21  |

|         | 3.2.1    | Memory space                               | 21  |

|         | 3.2.2    | I/O space                                  | 24  |

| 3.3     | Interna  | I Block Functions                          | 26  |

|         | 3.3.1    | Bus control unit (BCU)                     | 26  |

|         | 3.3.2    | Execution unit (EXU)                       | 28  |

| 3.4     | Logica   | Address and Physical Address               | 30  |

|         | 3.4.1    | Segment system                             | 30  |

|         | 3.4.2    | Segment configuration                      | 31  |

|         | 3.4.3    | Dynamic relocation                         | 34  |

| 3.5     | Effectiv | ve Address                                 | 36  |

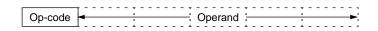

| 3.6 | Instructio | n Set                                           | 37 |

|-----|------------|-------------------------------------------------|----|

|     | 3.6.1      | List of instruction sets by function            | 37 |

|     | 3.6.2      | Format after instruction                        | 38 |

| 3.7 | Addressi   | ng Mode                                         | 38 |

|     | 3.7.1      | Instruction address                             | 38 |

|     | 3.7.2      | Data address                                    | 39 |

| 3.8 | Faster Ex  | ecution of Instructions                         | 43 |

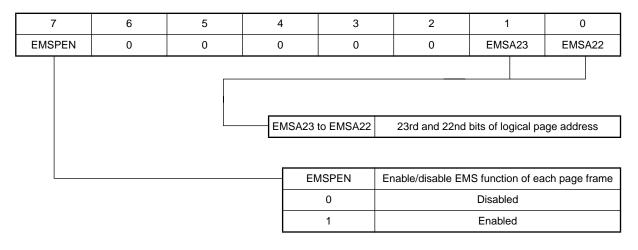

|     | 3.8.1      | Dual data bus system                            | 43 |

|     | 3.8.2      | Effective address generator (EAG)               | 44 |

|     | 3.8.3      | Temporary register/shifter A and B (TA, TB)     | 44 |

|     | 3.8.4      | Loop counter (LC)                               | 44 |

|     | 3.8.5      | Program counter (PC) and prefetch pointer (PFP) | 44 |

| 3.9 | EMS Fur    | nctions                                         | 45 |

|     | 3.9.1      | EMS control registers                           | 45 |

|     | 3.9.2      | Caution on accessing EMS control registers      | 48 |

|     | 3.9.3      | EMS setting example                             | 48 |

###

| 4.1 | Interface between V30MX and Memory    | 51 |

|-----|---------------------------------------|----|

|     | 4.1.1 Cautions on accessing word data |    |

| 4.2 | Accessing I/O Space                   |    |

| 4.3 | Read Timing of Memory and I/O         |    |

| 4.4 | Write Timing of Memory and I/O        |    |

| 4.5 | Bus Hold Function                     |    |

#

| 5.1 | Hardwar   | e Interrupt                                            | 64 |

|-----|-----------|--------------------------------------------------------|----|

|     | 5.1.1     | Non-maskable interrupt (NMI)                           | 64 |

|     | 5.1.2     | Maskable interrupt (INT)                               | 64 |

| 5.2 | Software  | Interrupts                                             | 67 |

| 5.3 | Timing a  | which Interrupt is Not Acknowledged                    | 68 |

| 5.4 | Interrupt | Servicing in Execution of Block Processing Instruction | 69 |

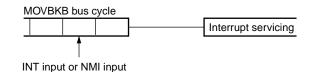

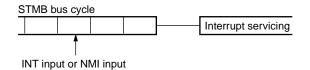

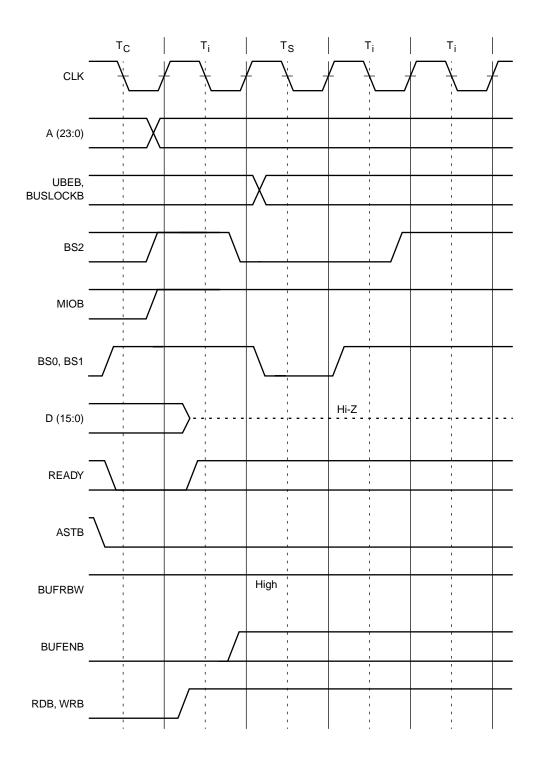

| CHAPTER | 6 ST/     | ANDBY FUNCTIONS                                            |

|---------|-----------|------------------------------------------------------------|

| 6.1     | Setting o | f Standby Mode                                             |

| 6.2     | Standby   | Mode                                                       |

| 6.3     | Release   | of Standby Mode73                                          |

|         | 6.3.1     | Release by hardware interrupt73                            |

|         | 6.3.2     | Release by RESET input73                                   |

|         |           | SET FUNCTIONS         75           ST FUNCTIONS         77 |

| 8.1     | Test Pins | 5                                                          |

|         | 8.1.1     | Test bus pins (TBI (27:0), TBO (71:0))                     |

|         | 8.1.2     | BUNRI, TEST                                                |

| 8.2     | Normal N  | Mode                                                       |

| 8.3     | Unit Test | Mode and Standby Test Mode                                 |

|         | 8.3.1     | Unit test mode                                             |

|         | 8.3.2     | Standby test mode78                                        |

## LIST OF FIGURES

Title, Page

Fig. No.

| 3-1  | Memory Map (when EMSREN = 0)                                               |    |

|------|----------------------------------------------------------------------------|----|

| 3-2  | Memory Map (when EMSREN = 1)                                               | 23 |

| 3-3  | I/O Map (when EMSREN = 0)                                                  |    |

| 3-4  | I/O Map (when EMSREN = 1)                                                  | 25 |

| 3-5  | Generation of Effective Address                                            |    |

| 3-6  | Conceptual Diagram of Segment System                                       | 30 |

| 3-7  | Relationship between Segment Register, Offset Address and Physical Address | 31 |

| 3-8  | Relationship between Each Segment Register, Segment and Memory Space       | 33 |

| 3-9  | Dynamic Relocation                                                         | 35 |

| 3-10 | Memory Address Calculation                                                 |    |

| 3-11 | Dual Data Bus System                                                       | 43 |

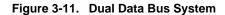

| 3-12 | EMS Control Register (EC)                                                  | 46 |

| 3-13 | EMS Data Register (EDL11 to EDL0, EDH11 to EDH0)                           | 47 |

| 3-14 | EMS Address Register (EMSPA7 to EMSPA2)                                    |    |

| 4-1  | Interface between V30MX and Memory                                         | 51 |

| 4-2  | Read Timing of Memory and I/O (1 wait)                                     | 54 |

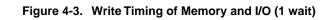

| 4-3  | Write Timing of Memory and I/O (1 wait)                                    | 56 |

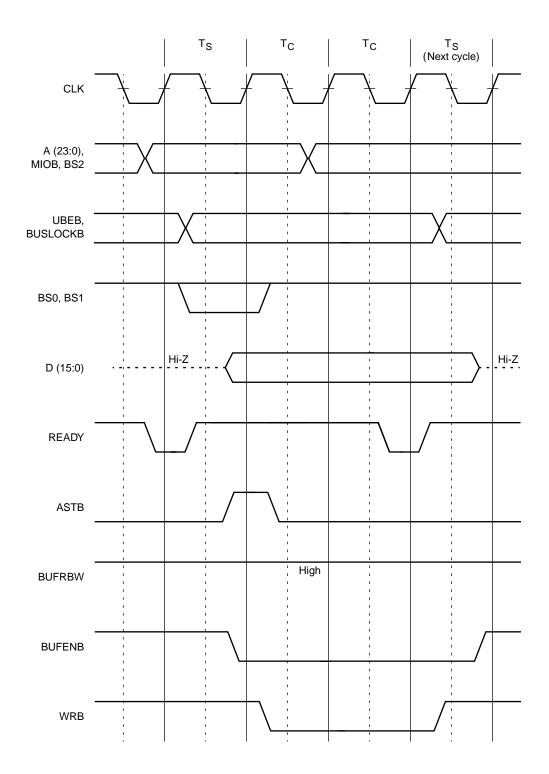

| 4-4  | Bus Hold Timing (Write Operation $\rightarrow$ Bus Hold State)             | 58 |

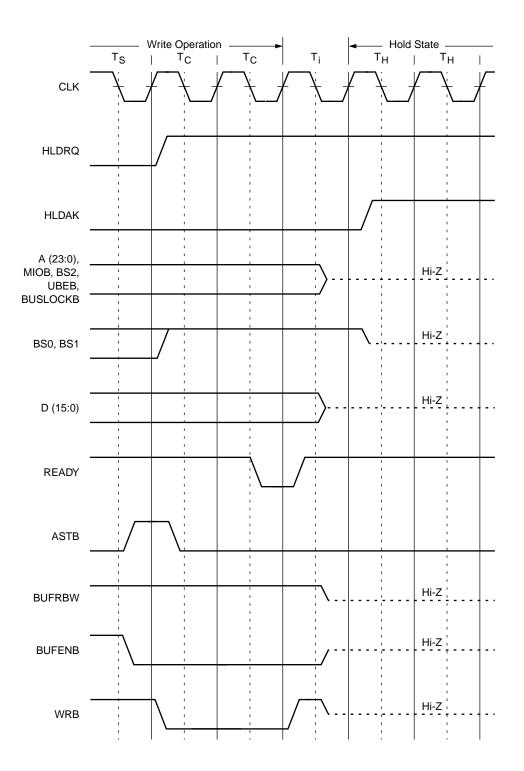

| 4-5  | Bus Hold Timing (Bus Hold State $\rightarrow$ Write Operation)             | 59 |

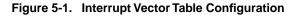

| 5-1  | Interrupt Vector Table Configuration                                       | 62 |

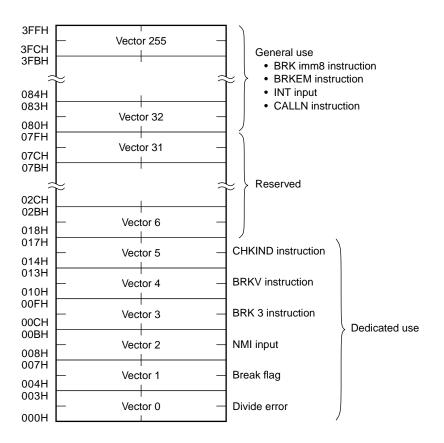

| 5-2  | Interrupt Acknowledge Cycle                                                | 65 |

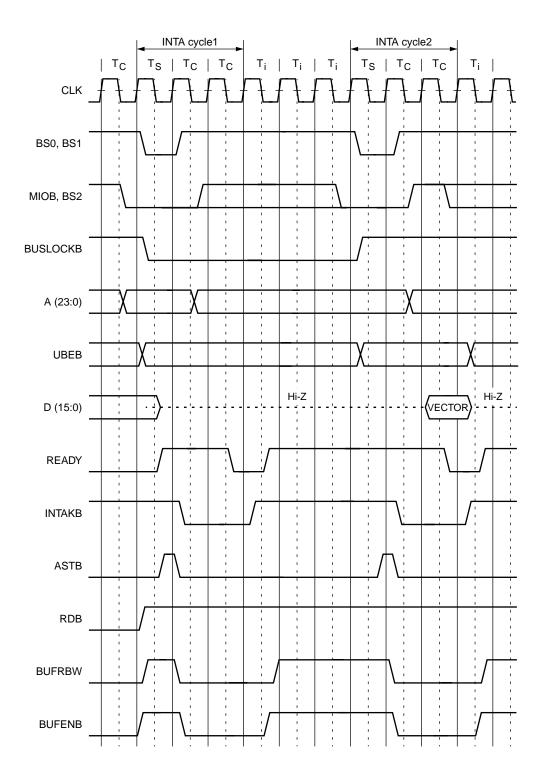

| 5-3  | Interrupt Acknowledge Cycle (with code fetch)                              | 66 |

| 6-1  | Timing in Standby Mode                                                     | 72 |

### LIST OF TABLES

| Table | No. Title, Page                                               |    |

|-------|---------------------------------------------------------------|----|

| 3-1   | Address and Data Configuration of Each Memory Element         | 22 |

| 3-2   | Segment Registers and Offset Addressing                       | 32 |

| 4-1   | V30MX Data Access                                             | 52 |

| 5-1   | Interrupt Source List                                         | 61 |

| 5-2   | Number of Bus Cycles Required until Interrupt is Acknowledged | 39 |

| 7-1   | Pin Status after Reset                                        | 75 |

| 7-2   | Initial Values of Registers after Reset                       | 76 |

| 8-1   | Test Mode Settings                                            | 77 |

#### CHAPTER 1 GENERAL DESCRIPTION

The V30MX core is a CPU core which separates addresses from the data bus of the  $\mu$ PD70116H (V30HL), an NEC generalpurpose microcomputer, improving bus efficiency and CPI (Cycle per Instruction) by 70 % compared with the V30HL. It also incorporates new registers that support the LIM EMS4.0.

The V30MX core has a complete static circuit configuration, which facilitates standby and clock stop and provides low power consumption.

Since the V30MX and V30HL use a common instruction set, existing programs can be used without changes.

#### 1.1 Features

- (1) A complete static circuit configuration facilitates standby and clock stop.

- (2) Low power consumption

- (3) Incorporates registers that support LIM EMS4.0.

- (4) Address space

- Memory : 1 M bytes (16 M bytes when using EMS)

- I/O : 64 K bytes

- (5) A variety of memory addressing modes

- (6)  $14 \times 16$ -bit register set

- (7) 101-command of instruction set (completely compatible with  $\mu$ PD70116H)

- Bit field manipulation instruction : Data transfer between bit field of bits 1 to 16 of memory and accumulator

- Packed BCD operation instruction : Addition, subtraction and comparison of 1 to 255-digit BCD string

- Bit manipulation instruction : Set, clear, inversion, and test of arbitrary bit of 8/16-bit register and memory

- (8) High-speed effective address calculation

#### 1.2 Outline of Differences from V30HL

- (1) In the V30HL, addresses and data are multiplexed and use the same pins. In the V30MX, they are separate pins. In addition, the address bus has been extended to 24 bits. Because of this, the V30MX has a bus timing different from the V30HL.

- (2) The V30MX is not provided with the function of switching between a small scale and large scale as in the V30HL. Signals like INTAK (OS1) that are output by switching between small and large scales in the V30HL are output from separate pins in the V30MX.

- (3) The following pins exist in the V30HL, but not in the V30MX.

- RQ/AK1, RQ/AK0, S/LG

- (4) The V30HL has a  $\mu$ PD8080AF emulation function, but the V30MX has no such function.

#### 1.3 Symbol Diagram

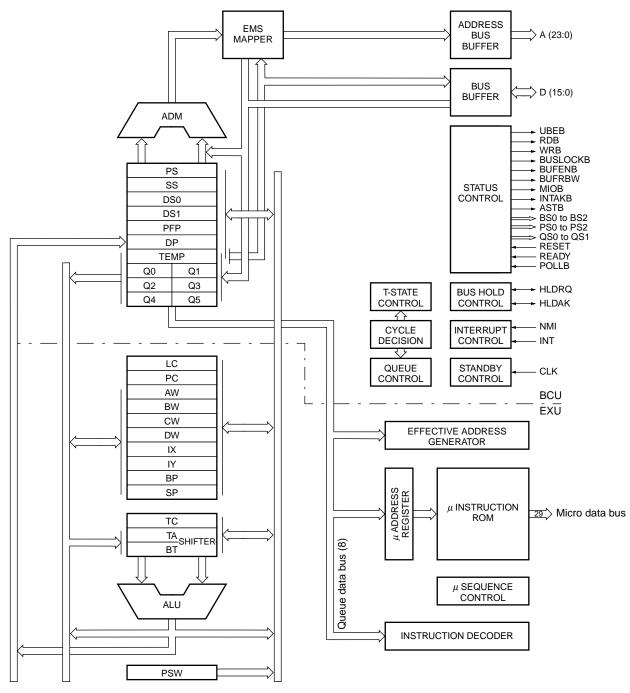

#### 1.4 Internal Block Diagram

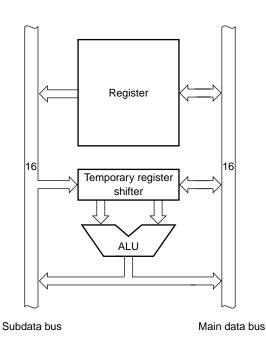

Subdata bus (16)

Main data bus (16)

[MEMO]

#### **CHAPTER 2 PIN FUNCTIONS**

This chapter describes the names and functions of the V30MX core pins.

#### 2.1 Pin List

| Pin Name   | Input/Output | Function                                 | Reference Item |

|------------|--------------|------------------------------------------|----------------|

| A (23:0)   | OZ           | Address                                  | 2.2 (1)        |

| D (15:0)   | I/O          | Data                                     | 2.2 (2)        |

| UBEB       | OZ           | Upper Byte Enable                        | 2.2 (3)        |

| RDB        | OZ           | Read                                     | 2.2 (4)        |

| READY      | I            | Bus Ready                                | 2.2 (5)        |

| INT        | I            | Interrupt Request                        | 2.2 (6)        |

| POLLB      | I            | Test                                     | 2.2 (7)        |

| NMI        | I            | Non Maskable Interrupt                   | 2.2 (8)        |

| RESET      | I            | Reset                                    | 2.2 (9)        |

| CLK        | I            | Clock                                    | 2.2 (10)       |

| QS0, QS1   | 0            | Queue Status                             | 2.2 (11)       |

| BUSLOCKB   | OZ           | Lock                                     | 2.2 (12)       |

| BS2 to BS0 | OZ           | Bus Cycle Status                         | 2.2 (13)       |

| MIOB       | OZ           | I/O Memory Select                        | 2.2 (14)       |

| PS0, PS1   | 0            | Processor Status (Segment Register)      | 2.2 (15)       |

| PS2        | 0            | Processor Status (PSW: interrupt)        | 2.2 (16)       |

| PS3        | 0            | Processor Status (Native/8080 emulation) | 2.2 (17)       |

| WRB        | OZ           | Write                                    | 2.2 (18)       |

| INTAKB     | 0            | Interrupt Acknowledge                    | 2.2 (19)       |

| ASTB       | 0            | Address Strobe                           | 2.2 (20)       |

| BUFRBW     | OZ           | Data Transmit Receive                    | 2.2 (21)       |

| BUFENB     | OZ           | Data Enable                              | 2.2 (22)       |

| HLDRQ      | I            | Hold Request                             | 2.2 (23)       |

| HLDAK      | 0            | Hold Acknolwedge                         | 2.2 (24)       |

| EMSREN     | I            | EMS Registers Access Enable              | 2.2 (25)       |

| CNT1, CNT2 | 0            | 3-state pin control                      | 2.2 (26)       |

| DC         | 0            | D15 to D0 control                        | 2.2 (27)       |

| BUNRI      | 1            | Test Bus control                         | 2.2 (28)       |

| TEST       | 1            | Test Bus control                         | 2.2 (29)       |

| TBI (27:0) | I            | Test Bus (Input) 2.2 (30)                |                |

| TBO (71:0) | OZ           | Test Bus (Output)         2.2 (31)       |                |

| EI (3:0)   | I            | NEC Reserved                             | 2.2 (32)       |

| EO (8:0)   | 0            | NEC Reserved                             | 2.2 (33)       |

| CLKO       | 0            | NEC Reserved                             | 2.2 (34)       |

I : Input pin

O : Output (dedicated) pin OZ : 3-state output pin

#### 2.2 Description of Pin Functions

#### (1) A (23:0) (3-state output) address

24-bit address bus.

The address is output a half clock before the bus cycle. Normally, only A (19:0) are used for output and A (23:20) are low. When the EMS function is used, these pins are all used as the outputs for all bits A (23:0).

#### (2) D (15:0) (3-state input/output) data

16-bit data bus.

Go to high impedance during hold acknowledge and interrupt acknowledge.

#### (3) UBEB (3-state output) upper byte enable

Indicates that the higher bits of D (15:0) (D (15:8)) are used in Tc of the bus cycle.

In the V30MX, memory and I/O are accessed separately for byte data banks which are accessed by an even address (A0 = 0) and for byte data banks which are accessed by an odd address (UBEB = 0) as shown in the table below.

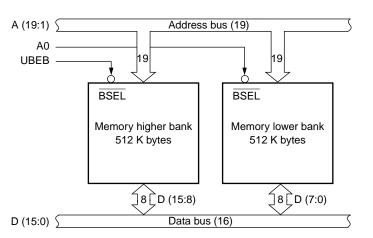

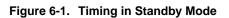

**Remark** The V30MX executes one bus cycle in at least 2 clocks. The first clock is called  $T_S$ , and the next clock  $T_C$ . When a wait is inserted,  $T_C$  is repeated until the next bus cycle is started.

| 0                    | UBEB          | A0 | Number of Bus Cycles |   |

|----------------------|---------------|----|----------------------|---|

| Address of even word | 0             | 0  | 1                    |   |

| Word at odd address  | 1st bus cycle | 0  | 1                    | 2 |

|                      | 2nd bus cycle | 0  | 0                    |   |

| Byte at even address | 1             | 0  | 1                    |   |

| Byte at odd address  | 1             | 1  | 1                    |   |

The UBEB signal is driven low continuously during interrupt acknowledge (word access at an even address is necessary due to a vector read).

This pin goes to high impedance during hold acknowledge, but because it incorporates a latch (level hold circuit) it holds the previous value until it is driven externally. In standby mode, it is fixed at high level output.

#### (4) RDB (3-state output) read

Outputs a signal which becomes active (low level) during a data read from memory. I/O and memory are distinguished by MIOB.

This pin goes to high impedance during hold acknowledge, but because it incorporates a latch (level hold circuit) it holds the previous value until it is driven externally. In standby mode, it is fixed at high level output.

#### (5) READY (input) bus read

Controls waits.

It is sampled at the end of each  $T_C$  cycle, that is, on a rise of CLK. When memory or I/O cannot complete a data read/ write operation, if the READY signal is driven high, the V30MX generates a  $T_C$  cycle and so the read/write cycle can be extended. When the READY signal is low, it goes to the next bus cycle.

# Caution If the READY signal does not satisfy the setup time or hold time, correct operation is not guaranteed, so establish synchronization using an external circuit.

#### (6) INT (input) interrupt request

Inputs an interrupt request signal which can be masked by software.

This signal is detected in the last clock cycle of an instruction, and if the interrupt is enabled (interrupt enable flag (IE) is set (1)) it is acknowledged.

The external device checks whether the INT interrupt request has been acknowledged by the INTAKB signal output from the V30MX. Therefore, keep the INT signal high until the first INTAKB signal is output.

The priority order of interrupt request signals is as follows.

#### INT < NMI < HLDRQ

For example, when an INT interrupt and NMI interrupt are generated simultaneously, the NMI interrupt takes precedence and the INT interrupt is not acknowledged. A hold request can be acknowledged even during INT acknowledge.

Remark The standby mode can also be released by an INT signal.

#### (7) POLLB (input) test

This is used to synchronize between execution of the V30MX program and operation of an external device.

POLLB is checked by the POLL instruction, and if it is low, the next instruction is started, and if it is high, POLLB input is checked for each clock cycle until it is driven low.

#### (8) NMI (input)

Inputs an interrupt request signal which cannot be masked by software.

The NMI signal is active at the rising edge and detected in any clock cycle, however, it starts interrupt servicing after the end of the instruction being executed.

The interrupt start address for this interrupt is determined by interrupt vector 2.

Keep the NMI signal high for at least 5 clock cycles after a rising edge.

When inputting NMI requests consecutively, keep NMI low for at least one clock cycle.

The priority order of interrupt request signals is as follows.

#### INT < NMI < HLDRQ

**Remark** The standby mode can also be released by an NMI signal.

#### (9) RESET (input) reset

Inputs a reset signal.

A RESET signal takes precedence over all operations, and after reset release the program at memory address FFFF0H starts (segment value: FFFFH, offset value: 0H).

Keep the RESET input pin active (high) for at least 4 clock cycles.

**Remark** The standby mode can also be released by a RESET signal.

#### (10) CLK (input) clock

External clock input.

The V30MX does not divide clocks internally. Therefore, input to this CLK pin and internal operation are performed at the same frequency. When this CLK input is stopped, the STOP mode is entered. The STOP mode can help to reduce power consumption drastically.

# Caution Stopping CLK input while RESET input is active (high) does not satisfy the power supply current specification. Be sure to stop CLK input when RESET input is inactive (low).

#### (11) QS0, QS1 (output) queue status

This is a status signal that notifies an instruction queue signal to off-chip.

The instruction queue status means a status in which the execution unit (EXU) accesses an instruction queue. Signals QS0 and QS1 are only valid in one clock cycle immediately after this queue access. The table below shows the relationship between QS0, QS1 and instruction queue status.

| QS0 | QS1 | Instruction Queue Status                         |

|-----|-----|--------------------------------------------------|

| 0   | 0   | No operation                                     |

| 1   | 0   | Fetch of 1st byte of instruction                 |

| 0   | 1   | Queue is empty.                                  |

| 1   | 1   | Fetch of 2nd and subsequent bytes of instruction |

#### (12) BUSLOCKB (3-state output) lock

During execution of one instruction following the BUSLOCK instruction, it outputs a signal requesting the other master CPU of the multi-processor system not to use the system bus. It also outputs the signal during interrupt acknowledge.

#### (13) BS0 to BS2 (3-state output) bus cycle status

#### (14) MIOB (3-state output) I/O memory select

BS0, BS1, BS2 and MIOB indicate bus statuses as shown in the table below. BS2 of the V30MX has the same output values as COD/INTA in the i80286.

| BS2 | MIOB | BS1 | BS0 | Bus Cycle                                     |

|-----|------|-----|-----|-----------------------------------------------|

| 0   | 0    | 0   | 0   | Interrupt acknowledge                         |

| 0   | 0    | 0   | 1   | No signal with this combination is generated. |

| 0   | 0    | 1   | 0   | No signal with this combination is generated. |

| 0   | 0    | 1   | 1   | Idle state                                    |

| 0   | 1    | 0   | 0   | HALT state                                    |

| 0   | 1    | 0   | 1   | Memory data read                              |

| 0   | 1    | 1   | 0   | Memory data write                             |

| 0   | 1    | 1   | 1   | Idle state                                    |

| 1   | 0    | 0   | 0   | No signal with this combination is generated. |

| 1   | 0    | 0   | 1   | I/O read                                      |

| 1   | 0    | 1   | 0   | I/O write                                     |

| 1   | 0    | 1   | 1   | Idle state                                    |

| 1   | 1    | 0   | 0   | No signal with this combination is generated. |

| 1   | 1    | 0   | 1   | Code fetch                                    |

| 1   | 1    | 1   | 0   | No signal with this combination is generated. |

| 1   | 1    | 1   | 1   | Idle state                                    |

#### (15) PS0, PS1 (output) processor status (segment register)

In the V30HL, addresses and processor statuses can be output at any time on a time sharing basis from A16/PS0 to A19/PS3, while in the V30MX they are output from different pins.

The PS0 and PS1 signals indicate which segment is currently used. The table below shows the relationship between PS0, PS1 and the segment.

| PS0 | PS1 | Segment         |  |  |  |  |  |  |

|-----|-----|-----------------|--|--|--|--|--|--|

| 0   | 0   | Data segment 1  |  |  |  |  |  |  |

| 1   | 0   | Stack segment   |  |  |  |  |  |  |

| 0   | 1   | Program segment |  |  |  |  |  |  |

| 1   | 1   | Data segment 0  |  |  |  |  |  |  |

#### (16) PS2 (output) processor status (PSW: interrupt)

The PS2 signal indicates the content of the interrupt enable flag (IE) of the program status word (PSW).

The table below shows the relationship between PS2 and IE.

| PS2 | IE Flag (PSW) | Status                 |

|-----|---------------|------------------------|

| 0   | 0             | INT interrupt enabled  |

| 1   | 1             | INT interrupt disabled |

#### (17) PS3 (output) processor status (native/8080 emulation)

This signal always outputs a low level.

The V30MX is not provided with the  $\mu$ PD8080AF emulation function.

#### (18) WRB (3-state output) write

Outputs a signal which becomes active (low) in a data write to I/O or memory.

I/O and memory are distinguished by MIOB.

This pin goes to high impedance during hold acknowledge, but since it incorporates a latch (level hold circuit), it holds the previous state until it is driven externally. In standby mode, it is fixed at high level output.

#### (19) INTAKB (output) interrupt acknowledge

Outputs an interrupt acknowledge signal.

The INTAKB signal is output when an INT signal is acknowledged, and the external device inputs the interrupt vector to the V30MX via the data bus in synchronization with this signal.

#### (20) ASTB (output) address strobe

Outputs a strobe signal to latch address information to off-chip. It is not activated during HALT status output (remains low).

#### (21) BUFRBW (3-state output) data transmit receive

Outputs a signal to determine the data transfer direction of the external bi-directional buffer.

The BUFRBW signal indicates transmission to the external device when it is high, and reception from the external device when it is low.

This pin goes to high impedance during hold acknowledge, but since it incorporates a latch (level hold circuit), it holds the previous state until it is driven externally. In standby mode, it is fixed at low level output.

#### (22) BUFENB (3-state output) data enable

Outputs an output enable signal for the external bi-directional buffer.

The BUFENB signal is output during data transfer from/to memory or I/O or during interrupt vector input.

This pin goes to high impedance during hold acknowledge, but since it incorporates a latch (level hold circuit), it holds the previous state until it is driven externally. In standby mode, it is fixed at high level output.

#### (23) HLDRQ (input) hold request

Inputs a signal from the external device to request the V30MX to release the address bus, data bus and control bus (bus hold).

The priority order among interrupt request signals and HLDRQ signal is as follows.

#### INT < NMI < HLDRQ

# Caution Since normal operation is not guaranteed unless the HLDRQ signal satisfies the setup time, establish synchronization using an external circuit.

#### (24) HLDAK (output) hold acknowledge

Outputs an acknowledge signal which indicates that a bus hold request signal (HLDRQ) has been acknowledged. While the HLDAK signal is active (high), the address bus, data bus, and 3-state output control bus go to high impedance.

#### (25) EMSREN (input) EMS registers access enable

Enables/disables access to the I/O mapped register for the EMS function control. When EMSREN is high, access to the I/O mapped register is enabled. Access is also enabled to the same external I/O address as the I/O address assigned to the register.

# Caution EMSREN can be changed only after a reset. At other timings the operation of the V30MX is not guaranteed.

#### (26) CNT1, CNT2 (output) 3-state pin control

#### (27) DC (output) D (15:0) control

CNT1 is used for control of the 3-state pins A (23:0), BS2, MIOB, UBEB, BUSLOCKB, RDB, WRB, BUFENB, and BUFRBW.

CNT2 is used for direction control of 3-state pins BS1 and BS0.

DC is used for direction control of input/output pins D (15:0).

The relationship between respective pins and control signals is shown below.

| Pin to be Controlled                 | CNT1 | Status         |

|--------------------------------------|------|----------------|

| A (23:0), BS2, MIOB, UBEB, BUSLOCKB, | Н    | High impedance |

| RDB, WRB, BUFENB, BUFRBW             | L    | Output active  |

| Pin to be Controlled | CNT2 | Status         |

|----------------------|------|----------------|

| BS1, BS0             | Н    | High impedance |

|                      | L    | Output active  |

| Pin to be Controlled | DC | Status      |

|----------------------|----|-------------|

| D (15:0)             | Н  | Input mode  |

|                      | L  | Output mode |

- (28) BUNRI (input) test bus control

- (29) TEST (input) test bus control

- (30) TBI (27:0) (input) test bus (input)

- (31) TBO (71:0) (3-state output) test bus (output)

These pins are used for mega-function separation tests using the test bus.

For details of using these pins, refer to CHAPTER 8 TEST FUNCTIONS.

#### (32) EI (3:0) (input) NEC reserved

These pins are reserved for NEC.

Be sure to use F091 to input the levels shown in the table below.

| EIO | Н |

|-----|---|

| El1 | н |

| El2 | н |

| El3 | L |

#### (33) EO (8:0) (output) NEC reserved

These pins are reserved for NEC.

Leave these pins open.

#### (34) CLKO (output) NEC reserved

These pins are reserved for NEC.

Leave these pins open.

### 2.3 Pin Information in Specific Status

|            |             | Normal Mode       |             | Test                                 | Mode                                   |  |

|------------|-------------|-------------------|-------------|--------------------------------------|----------------------------------------|--|

| Pin        | During HOLD | During HALT       | After Reset | Standby<br>(BUNRI = 1)<br>(TEST = 0) | Unit Test<br>(BUNRI = 1)<br>(TEST = 1) |  |

| A (23:0)   | Hi-Z        | Continuous        | Hi-Z        | Hi-Z                                 | Hi-Z                                   |  |

| D (15:0)   | Hi-Z        | Continuous        | Hi-Z        | Hi-Z                                 | Hi-Z                                   |  |

| UBEB       | Hi-Z        | Н                 | Hi-Z        | Continuous                           | Х                                      |  |

| RDB        | Hi-Z        | Н                 | Hi-Z        | Continuous                           | Х                                      |  |

| QS0, QS1   | L           | L                 | L           | Continuous                           | Х                                      |  |

| BUSLOCKB   | Hi-Z        | H <sup>Note</sup> | Hi-Z        | Continuous                           | Х                                      |  |

| BS2 to BS0 | Hi-Z        | L                 | Hi-Z        | Continuous                           | Х                                      |  |

| МІОВ       | Hi-Z        | Н                 | Hi-Z        | Continuous                           | Х                                      |  |

| PS0        | Continuous  | Continuous        | L           | Continuous                           | Х                                      |  |

| PS1        | Continuous  | Continuous        | Н           | Continuous                           | Х                                      |  |

| PS2        | Continuous  | Continuous        | L           | Continuous                           | Х                                      |  |

| PS3        | Continuous  | Continuous        | L           | Continuous                           | Х                                      |  |

| WRB        | Hi-Z        | Н                 | Hi-Z        | Continuous                           | Х                                      |  |

| INTAKB     | Н           | Н                 | Н           | Continuous                           | X<br>X                                 |  |

| ASTB       | L           | L                 | L           | Continuous                           |                                        |  |

| BUFRBW     | Hi-Z        | Continuous        | Hi-Z        | Continuous                           | Х                                      |  |

| BUFENB     | Hi-Z        | Н                 | Hi-Z        | Continuous                           | Х                                      |  |

| HLDAK      | н           | L                 | L           | Continuous                           | Х                                      |  |

| DC         | н           | Continuous        | Н           | Continuous                           | Х                                      |  |

| CNT1, CNT2 | Н           | Continuous        | Н           | Continuous                           | Х                                      |  |

| TBO (71:0) | Hi-Z        | Hi-Z              | Hi-Z        | Hi-Z                                 | Output                                 |  |

Note If a BUSLOCK instruction is executed before a HALT instruction, a low level is output.

**Remarks** 1. "Continuous" in the table indicates that the previous operation is continued. 2. "Standby" in the test mode refers to the standby test mode (refer to CHAPTER 8 TEST FUNCTIONS).

3. X : Don't care

[MEMO]

#### **CHAPTER 3 CPU FUNCTIONS**

#### 3.1 Register Configuration

#### 3.1.1 General-purpose registers (AW, BW, CW, DW)

There are four 16-bit registers. These can be not only used as 16-bit registers, but also accessed as 8-bit registers (AH, AL, BH, BL, CH, CL, DH, DL) by dividing each register into the higher 8 bits and the lower 8 bits.

Therefore, these registers are used as 8-bit registers or 16-bit registers for a wide range of instructions such as transfer instruction, arithmetic operation instruction, logical operation instruction.

Furthermore, the following registers are used as the default registers for specific instruction processing.

- AW : Word multiplication/division, word input/output, data change

- AL : Byte multiplication/division, byte input/output, BCD rotate, data conversion

- AH : Byte multiplication/division

- BW : Data conversion

- CW : Loop control branch, repeat, prefix

- CL : Shift instruction, rotation instruction, BCD operation

- DW : Word multiplication/division, indirect addressing input

#### 3.1.2 Segment registers (PS, SS, DS0, DS1)

The V30MX can divide the memory space into logical segments in 64 K-byte units and control up to 4 segments simultaneously (segment system). The start address of each segment is specified by the following 4 segment registers.

- Program segment register (PS) : Specifies the base address of the segment that stores instructions.

- Stack segment register (SS) : Specifies the base address of the segment that performs stack operations.

- Data segment 0 register (DS0) : Specifies the base address of the segment that stores data.

- Data segment 1 register (DS1) : Specifies the base address of the segment that is used as a data destination by data transfer instructions.

For details of the segment system and segment registers, refer to 3.4 Logical Address and Physical Address.

#### 3.1.3 Pointer (SP, BP)

The pointer consists of two 16-bit registers (stack pointer (SP) and base pointer (BP)).

Each register is used as a pointer to specify a memory address and can be referenced in an instruction and is also used as an index register during a memory data reference.

The SP indicates the address in the stack segment at which the latest data is stored and is used as the default register during stack operation.

The BP is used to fetch the data stored on the stack.

#### 3.1.4 Program counter (PC)

The PC is a 16-bit binary counter that holds the offset information of the memory address of the program which the execution unit (EXU) is about to execute.

The PC value is automatically incremented (+1) every time the microprogram fetches an instruction byte from an instruction queue.

Furthermore, in execution of a branch instruction, call instruction, return instruction and break instruction, a new location is loaded and the PC value becomes the same as that of the prefetch pointer (PFP).

#### 3.1.5 Program status word (PSW)

The PSW consists of 6 kinds of status flag and 4 kinds of control flag.

#### Status flag

| Carry flag (CY)           | Refer to <b>(a)</b> . |

|---------------------------|-----------------------|

| Parity flag (P)           | Refer to <b>(b)</b> . |

| Auxiliary carry flag (AC) | Refer to <b>(c)</b> . |

| Zero flag (Z)             | Refer to (d).         |

| Sign flag (S)             | Refer to <b>(e)</b> . |

| Overflow flag (V)         | Refer to (f).         |

#### **Control flag**

| Break flag (BRK)           | Refer to <b>(g)</b> . |

|----------------------------|-----------------------|

| Interrupt enable flag (IE) | Refer to <b>(h)</b> . |

| Direction flag (DIR)       | Refer to (i).         |

| Mode flag (MD)             | Refer to (j).         |

The status flag is automatically set (1) and reset (0) according to the execution result (data value) of each instruction.

The CY flag can directly be set/reset or inverted by an instruction. The control flag is set/reset by an instruction and controls the operation of the V30MX.

The IE flag and BRK flag are reset when interrupt servicing is started.

RESET input resets (0) all flags (except MD flag).

The PSW is manipulated in byte units or word units by the processing shown below. Processing in byte units is only carried out on the lower 8 bits (including the status flags except the V flag).

|   | 15 | 14 | 13 | 12 | 11 | 10  | 9  | 8   | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0  |

|---|----|----|----|----|----|-----|----|-----|---|---|---|----|---|---|---|----|

| Γ | MD | 1  | 1  | 1  | V  | DIR | IE | BRK | S | Z | 0 | AC | 0 | Р | 1 | CY |

Bits 0 to 7 can be stored or restored in AH by a MOV instruction.

All bits of the PSW are saved to the stack when an interrupt is generated or in execution of a call instruction and restored by a return instruction (RETI, RETM).

The PSW can be saved or restored to the stack independently by a PUSH PSW instruction or POP PSW instruction.

The flags are set to the states shown below after execution of each instruction.

#### (a) Carry flag (CY)

< 1 > Binary addition/subtraction

In the case of processing in byte units, CY is set when there is a carry or borrow from operation result bit 7, and reset otherwise.

In the case of word operation, CY is set when there is a carry or borrow from operation result bit 15, and reset otherwise. It is not changed by an increment or decrement instruction.

< 2 > Logical operation

CY is reset without regard to the operation result.

< 3 > Binary multiplication

CY is reset if AH is other than 0 as a result of an unsigned byte operation.

CY is reset if AH is AL sign extension as a result of a signed byte operation and set otherwise.

CY is reset if DW is 0 as a result of an unsigned word operation and set otherwise.

CY is reset if DW is AW sign extension as a result of an unsigned word operation and set otherwise.

In the case of an 8-bit immediate operation, CY is reset when the product is within 16 bits and set otherwise.

< 4 > Binary division

Undefined

< 5 > Shift/rotate

In the case of a shift or rotate including the CY flag, CY is set when the bit shifted to the CY flag is 1 and reset if 0.

#### (b) Parity flag (P)

< 1 > Binary addition/subtraction, logical operation, shift

Set when the number of "1" bits of the lower 8 bits of the operation result is even and reset when it is odd.

Set when the result is all "0".

< 2 > Binary multiplication/subtraction

Undefined

#### (c) Auxiliary carry flag (AC)

< 1 > Binary addition/subtraction

In the case of processing in byte units, it is set when there is a carry from the lower 4 bits to the higher 4 bits or a borrow from the higher 4 bits to the lower 4 bits, and reset otherwise.

In a word operation, it performs the same operation as for a byte operation with respect to the lower bytes.

< 2 > Logical operation, binary multiplication/division, shift/rotate

Undefined

#### (d) Zero flag (Z)

< 1 > Binary addition/subtraction, logical operation, shift/rotate

It is set when the 8 bits and 16 bits of the result are all 0 for a byte operation and word operation, respectively, and reset otherwise.

< 2 > Binary multiplication/division

Undefined

#### (e) Sign flag (S)

< 1 > Binary addition/subtraction, logical operation, shift/rotate

Set when bit 7 of the result is 1 and reset when it is 0 in the case of a byte operation.

Set when bit 15 of the result is 1 and reset when it is 0 in the case of a word operation.

< 2 > Binary multiplication/division

Undefined

#### (f) Overflow flag (V)

< 1 > Binary addition/subtraction

Set when carries from bit 7 and bit 6 are different and reset when they are the same in the case of a byte operation.

Set when carries from bit 15 and bit 14 are different and reset when they are the same in the case of a word operation.

#### < 2 > Binary multiplication

As a result of an unsigned byte operation, reset if AH is 0 and set otherwise.

As a result of a signed byte operation, reset if AH is sign extension of AL and set otherwise.

As a result of an unsigned word operation, reset if DW is 0 and set otherwise.

As a result of a signed word operation, reset if DW is sign extension of AW and set otherwise.

In the case of an 8-bit immediate operation, reset if the product is within 16 bits and set if the product exceeds 16 bits.

< 3 > Binary division

Reset.

< 4 > Logical operation

Reset.

< 5 > Shift/rotate

In the case of a left 1-bit shift/rotate, the status of the overflow flag is as follows depending on the operation result.

When CY = MSB: Reset When CY  $\neq$  MSB: Set

In the case of a right 1-bit shift/rotate, its status is as follows depending on the operation result.

When MSB = next lower bit of MSB: Reset When MSB  $\neq$  next lower bit of MSB: Set

In the case of a multi-bit shift/rotate, it is undefined.

#### (g) Break flag (BRK)

Only when it is saved to the stack as part of the PSW, it can be set by a memory manipulation instruction, and becomes valid when restored to the PSW after it is set.

If the BRK flag is set, executing one instruction automatically generates an software interrupt (interrupt vector 1) allowing tracing of one instruction at a time.

#### (h) Interrupt enable flag (IE)

IE is set by an EI instruction and the INT interrupt is enabled. It is reset by a DI instruction and the INT interrupt is disabled.

#### (i) Direction flag (DIR)

Set by a SET1 DIR instruction and reset by a CLR1 DIR instruction.

When the DIR flag is set, processing is carried out from the higher addresses to the lower addresses in block transfer/ input/output type instructions. When it is reset, processing is carried out from the lower addresses to the higher addresses.

#### (j) Mode flag (MD)

This is a  $\mu$ PD8080AF emulation function related flag which conforms to the previous V30HL. Since the V30MX is not provided with the emulation function, this flag is invalid.

#### 3.1.6 Index register (IX, IY)

This consists of two 16-bit registers (IX, IY). In a memory data reference, it is used as an index register to generate effective addresses (each register can also be referenced in an instruction).

Furthermore, in specific instruction processing, it has the following special roles.

- IX: Address register for source operand in block data manipulation instruction Base register in variable length bit field manipulation instruction Address register for source operand in BCD string operation instruction

- IY: Address register for destination operand in block data manipulation Base register in variable length bit field manipulation Address register for destination operand in BCD string operation instruction

#### 3.2 Address Space

#### 3.2.1 Memory space

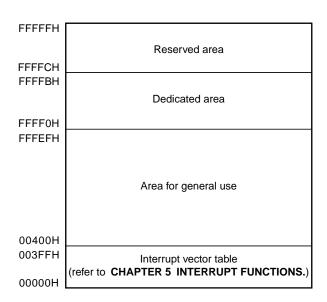

#### <1 > When low level is input to EMSREN pin (when EMS is not used)

The V30MX uses 20-bit address information and can access 1 M (512 K word) of memory. The start address after a reset is FFFF0H.

Figure 3-1 shows the memory map. The 1 K bytes from 00000H to 003FFH are allocated to the interrupt vector table. However, the table area that is not used by the system can be used for other purposes. The 12 bytes from FFFF0H to FFFFBH are automatically used for a reset start, etc., and cannot be used for other purposes. The 4 bytes from FFFFCH to FFFFFH are also reserved for future use and are not available to users.

Figure 3-1. Memory Map (when EMSREN = 0)

The elements stored in the memory area include operation codes, interrupt start addresses, stack data, general variables, and consist of two kinds; byte units and word units.

Addresses generated by an instruction for these elements can be even (A0 = 0) or odd  $(A0 = 1)^{Note}$ . Word data in the V30MX is designed to be accessible for both even and odd addresses. Both even and odd addresses are possible for generation of an instruction. For the access method, refer to the memory space access method.

**Note** This excludes the case where the address of the area in which the interrupt start address (interrupt vector table) is stored is always even (A0 = 0).

Table 3-1 shows the address and data configuration of each memory element.

| Memory Element         | Address  | Data Configuration    |

|------------------------|----------|-----------------------|

| Operation code         | Even/odd | 1 to 6 bytes          |

| Interrupt vector table | Even     | 2 words/vector        |

| Stack                  | Even/odd | Word                  |

| General variable       | Even/odd | Byte/word/double word |

#### Table 3-1. Address and Data Configuration of Each Memory Element

The word data configuration and double data configuration are as follows.

#### Word data configuration

#### Double word data configuration

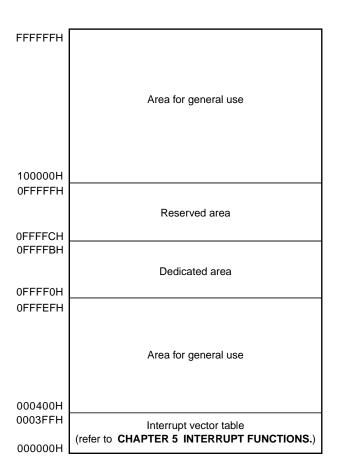

#### < 2 > When high level is input to EMSREN pin (when EMS is used)

When EMS is used, the address space becomes 16 M (24 bits).

The mapping sources for memory extension are 80000H to 9FFFFH (fixed), C0000H to CFFFFH, D0000H to DFFFFH and E0000H to EFFFFH (selected from these ranges). The mapping destinations are determined by setting the EMS data register (refer to **3.9 EMS Functions**).

The area 000000H to 0FFFFFH is the same as the case where EMS is not used.

The start address after a reset is 0FFFF0H whether the EMS function is used or not.

Figure 3-2. Memory Map (when EMSREN = 1)

#### 3.2.2 I/O space

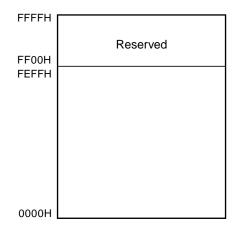

The V30MX can access an I/O space of up to 64 K bytes (32 K words) in an area independent of the memory space.

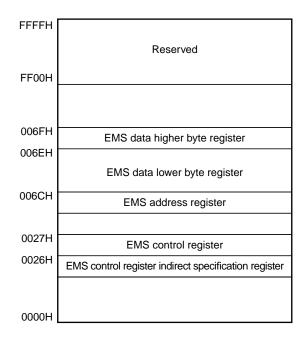

The I/O space is addressed by I/O address information output from the lower 16 bits of the address bus. Figure 3-3 and Figure 3-4 show I/O maps. The 256 bytes of FF00H to FFFFH are reserved for future use and are not available to users.

#### <1> When low level is input to EMSREN pin (when EMS is not used)

Figure 3-3. I/O Map (when EMSREN = 0)

#### < 2 > When high level is input to EMSREN pin (when EMS is used)

Each register for EMS control is placed in the I/O space and is accessed by an input/output instruction. Writing 01H to the EMS control register indirect specification register (0026H) beforehand allows the EMS control register to be accessed. All the 8 bits of the EMS control register indirect specification register are valid and initialized to 00H after a reset.

For the I/O addresses of these registers, only the lower 10 bits are decoded and the higher 6 bits are not decoded. Therefore, in software it operates so that the same internal I/O exists in multiple addresses.

Figure 3-4. I/O Map (when EMSREN = 1)

# 3.3 Internal Block Functions

The V30MX can be divided roughly into 2 processing units; the execution unit (EXU) and bus control unit (BCU). Each unit operates asynchronously, independent of the other, thus improving bus utilization efficiency and achieving high-speed execution of instructions.

#### 3.3.1 Bus control unit (BCU)

The BCU has the following functions.

#### • Instruction prefetch

Performs prefetch of instructions using the prefetch queue (Q5 to Q0).

Prefetch means pre-loading of the next instruction to be executed while the bus is free during execution of an instruction.

The BCU of the V30MX carries out prefetch automatically when there are a lot of free spaces in the queue.

#### · Control of external address/data bus

Drives the bus in response to a request from the EXU.

#### · Control of internal/external control functions

Controls the interrupt function, bus hold function and standby function.

The function of each BCU block is as follows.

#### (1) Prefetch pointer (PFP)

This is a 16-bit binary counter to hold the offset information of the program memory address that the BCU is about to prefetch in the instruction queue.

The PFP is incremented (+1) every time an instruction byte is prefetched from the program memory. Furthermore, in execution of a branch, call, return or break instruction, a new location is loaded and the PFP value becomes the same as that of the program counter (PC).

The PFP is always used together with the program segment (PS).

#### (2) Prefetch queue (Q5 to Q0)

Provided with 6-byte instruction queue (FIFO), it can store a maximum of 6 bytes of an operation code that is prefetched by the BCU.

The operation code stored in the queue is fetched and executed by the EXU.

In execution of a branch, call, return or break instruction or servicing of an external interrupt, the content of the queue is cleared and an instruction at a new location is prefetched.

Normally, a prefetch is carried out when there is a free space of one word (2 bytes) or more. If the average execution time of instructions that are executed consecutively is greater than the number of clocks necessary to prefetch each operation code to some degree, operation codes that can be executed by the EXU are ready in the queue every time the EXU completes execution of one instruction, and it is possible to omit the time for fetch from memory from the instruction execution time. As a result, this improves the processing speed compared to other CPUs that fetch and execute one instruction at a time.

#### Caution In the following cases, the effect of the queue is reduced.

- When there are many instructions in which the queues are cleared as with execution of branch instructions

- · When there are a series of instructions with short execution time

#### (3) Data pointer (DP)

This is a 16-bit register pointing to read/write addresses of variables.

The register contents including the effective addresses generated by the effective address generator (EAG) and offset values of the memory addresses are transferred to the DP.

#### (4) Communication temporary register (TEMP)

This is a 16-bit temporary register for communications between the external data bus and EXU. Since TEMP uses byte accesses, it can read/write the higher byte and lower byte separately.

Basically, the EXU ends a write operation by carrying out data transfer to TEMP and ends a read operation after conforming that data is transferred from the external data bus to TEMP.

#### (5) Address modification circuit (ADM)

Performs generation of physical addresses (addition of segment register and prefetch pointer (PFP) or data pointer (DP)) and increments (+1) of the PFP.

### (6) Bus buffer

Performs signal output to the external address bus and signal input/output with the external data bus.

#### (7) Status controller

Determines the internal state and bus state, transmits them to each internal block and generates signals output to offchip.

#### (8) Bus hold controller

When there is a signal requesting bus release from off-chip, it controls each bus corresponding to the signal.

#### (9) Interrupt controller

Carries out servicing necessary for an interrupt request from off-chip.

#### (10) Standby controller

In standby mode, supplies a clock only to the circuits related to the function necessary to release the bus hold function and standby mode and stops other functions.

Furthermore, performs control when the system returns to the normal state if necessary.

# 3.3.2 Execution unit (EXU)

The EXU decodes instructions prefetched by the BCU and executes them by microprogram control. The function of each EXU block is as follows.

#### (1) Arithmetic and logical unit (ALU)

Consists of a full adder and logical operation circuit and executes arithmetic operations (addition/subtraction, multiplication/division, increment/decrement, auxiliary operations) and logical operations (test, AND, OR, XOR and bit-wise testing, set, clear, inversion).

#### (2) Temporary register/shifter A/B (TA/TB)

This is a 16-bit temporary register/shifter used for multiplication/division and shift/rotate (including BCD rotate) instructions.

In execution of multiplication/division instructions, operates as a TA+TB 32-bit temporary register/shifter, and in execution of shift/rotate instructions, only TB operates as a 16-bit temporary register/shifter.

Both TA and TB can read/write separately the higher byte and lower byte from/to the internal bus.

TA/TB holds ALU data.

#### (3) Temporary register C (TC)

This is a 16-bit temporary register used for multiplication/division and other internal processing.

TC holds ALU data.

#### (4) Loop counter (LC)

This is a 16-bit register which counts the number of loops of primitive block transfer and input/output instructions (MOVBK, OUTM, etc.) controlled by repeat prefix instructions (REP, REPC, etc.), the number of shifts of multi-bit shift/ rotate instructions.

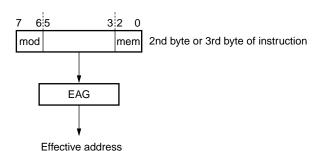

#### (5) Effective address generator (EAG)

This is a circuit which performs high-speed calculation of effective addresses necessary in memory accesses. Ends calculations in 2 clocks for all addressing modes.

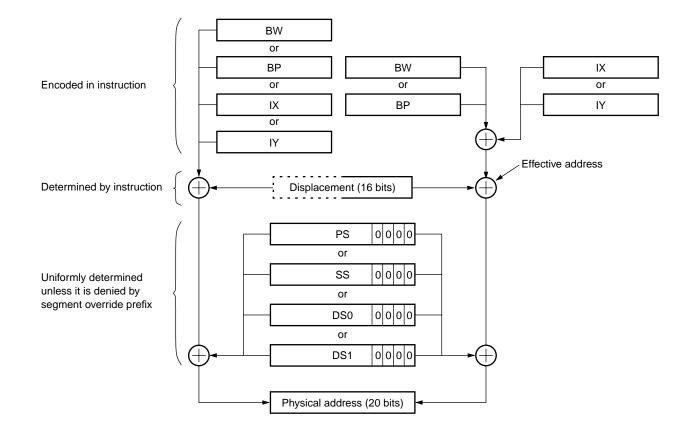

#### Figure 3-5. Generation of Effective Address

Fetches the byte (2nd or 3rd byte) specifying an instruction operand, generates a control signal about ALC and corresponding register manipulation if a memory access is required, and calculates the effective address and transfers it to the data pointer (DP).

Furthermore, performs control requesting startup of a bus cycle (memory read) to the BCU if necessary.

#### (6) Instruction decoder

Classifies the 1st byte of an operation code into a group with a specific function and holds it during execution of a micro instruction.

### (7) Micro address register

Specifies the ROM address of the next micro instruction to be executed. At the start of execution of a micro instruction, fetches the 1st byte of an instruction stored in the queue as the start address to this register and specifies the start address of the prescribed micro instruction sequence.

#### (8) Micro instruction ROM

Holds 1024 words of a 29-bit micro instruction.

#### (9) Micro instruction sequence circuit

Controls micro address registers, outputs of the micro instruction ROM and synchronization between the EXU and BCU.

# 3.4 Logical Address and Physical Address

There are two kinds of memory space address; logical address and physical address.

The physical address means an address that directly corresponds to hardware. The V30MX can access a 1 M-byte memory space and so the range of a physical address value is 00000H to FFFFFH. A physical address is generated every time the bus control unit (BCU) is started which fetches an instruction and transfers data, etc.

The logical address means an address used for addressing in the segment system.

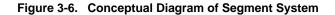

#### 3.4.1 Segment system

The segment means an address space in small units (MAX. 64 K bytes) which do not directly depend on program creation.

Each segment consists of continuous memory and can be specified individually.

Physical addresses cannot be controlled directly in program creation in machine language. The V30MX specifies memory addresses in a segment system.

Addressing in the segment system uses the following two types of address.

Segment base address : Start address of segment (address in 1 M-byte memory space) Offset address : Address allocated to each segment

In the segment system, the segment base address is fixed as a reference point and only the offset address is treated as an address in processing within each segment.

The segment base address is specified by the segment register.

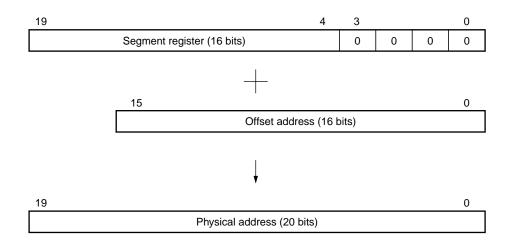

The physical address is a sum of the segment base address and offset address. Figure 3-7 shows the relationship between the segment register, offset address and physical address.

Figure 3-7. Relationship between Segment Register, Offset Address and Physical Address

As shown in Figure 3-7, the physical address is a sum of 16 times the segment register content (4 bits shifted to left) and offset value. At this time, the segment register content and offset value are treated as unsigned data.

In a program which is created as a set of multiple segments for which allocation addresses are specified by physical addresses, each segment is compiled and assembled individually and becomes one or a number of object modules. Each object module has a segment name, size, content classification, control information, etc., and becomes a parameter in execution of link processing.

Multiple object modules are linked and the segment base addresses corresponding the physical addresses are specified and become ready to be loaded to actual memory.

# 3.4.2 Segment configuration

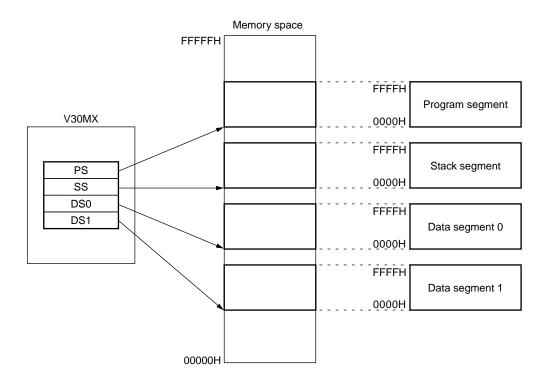

The V30MX can distinguish 4 kinds of segment(program, stack data 0, data 1) and define them. For each segment the start address is specified by one of the following 4 segment registers.

The BCU uses different segment registers for generation of physical addresses depending on the type of memory bus cycle.

- Program segment register (PS)

- Stack segment register (SS)

- Data segment 0 register (DS0)

- Data segment 1 register (DS1)

The offset address within each segment is specified by a specific register or effective address. Table 3-2 shows correspondence between each segment register and offset addressing.

| Segment Register<br>Offset                | Default | Overwrite    |

|-------------------------------------------|---------|--------------|

| PFP                                       | PS      | Disabled     |

| SP                                        | SS      | Disabled     |

| Effective address (BP base)               |         | PS, DS0, DS1 |

| Effective address (non-BP base)           | DS0     | PS, SS, DS1  |

| IX in instruction group A <sup>Note</sup> |         |              |

| IY in instruction group B <sup>Note</sup> | DS1     | Disabled     |

Table 3-2. Segment Registers and Offset Addressing

**Note** Instruction group A: Primitive block transfer instruction, primitive output instruction, BCD string instruction, EXT instruction

Instruction group B: Primitive block transfer instruction, primitive input instruction, BCD string instruction, INS instruction

When the default offset is a prefetch pointer (PFP), stack pointer (SP) and index register (IY) in instruction group B, the segment registers that can be combined are fixed at PS, SS, and DS1 respectively, and other segment registers cannot be used.

For other default offsets, any segment registers other than the default segment register can be specified by the segment override prefix.

Figure 3-8 shows the relationship between each segment register, segment and memory space.

Figure 3-8. Relationship between Each Segment Register, Segment and Memory Space

#### (1) Program segment

The start address of this segment is determined by the program segment register (PS) and the offset from the start address is specified by the prefetch pointer (PFP).

In this segment, an operation code, table data, etc., are placed.

By using the segment override prefix (PS:), the program segment can be used as the general variable area and source data area in execution of instruction group A.

#### (2) Stack segment

The start address of this segment is determined by the stack segment register (SS) and the offset from the start address is specified by the effective address when the stack pointer (SP) and base pointer (BP) as the base address are used.

This is used as an area to save the contents of the return address (PS, PC content), program status word (PSW), general register, etc., as a parameter transfer area and local variable area.

By using the segment override prefix (SS:), the stack segment can be used as a general variable area and source data area in execution of instruction group A.

#### (3) Data segment 0

The start address of this segment is determined by the data segment 0 register (DS0) and the offset from the start address is specified by the effective address when BP is not used as a base address.

This segment is used as an area to store general variables.

When executing instruction group A, it is used as a source data area. However, in this case, the content of the index register (IX) becomes the offset.

For the effective address when BP is used as the base address, the stack segment is used as the default, but data segment 0 can be used if the segment override prefix (DS0:) is used.

#### (4) Data segment 1

The start address of this segment is determined by the data segment 1 register (DS1). This can be used as a destination data area when executing instruction group B. In this case, the content of the index register (IY) becomes the offset.

If the segment override prefix (DS1:) is used, data segment 1 can be used as a general variable area or source data area in execution of instruction group A.

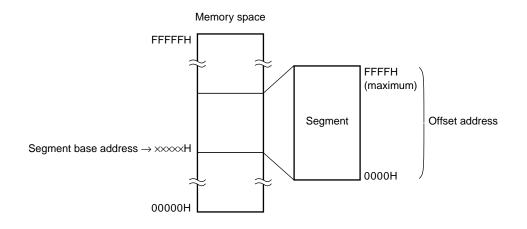

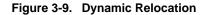

#### 3.4.3 Dynamic relocation

Relocating programs that are stored in two or more files separately in empty memory spaces for each execution is called dynamic relocation.

Figure 3-9 shows a conceptual diagram of dynamic relocation.

For the V30MX, memory addressing of a program can be determined only with the offset value for the base address of each segment (specified by each segment register). Therefore, it is possible to allocate the program in an arbitrary memory space by only adjusting to the physical address of the memory at which it is to be allocated (however, this is only possible if the base address of each segment is not changed in the program). This increases the degree of freedom of program allocation in the memory (addressing is possible in 16-byte units), enabling more effective utilization of memory and making it easier to implement a system that executes multiple jobs and tasks.

This can be applied to executing a program in a file on an external storage medium such as a floppy disk and hard disk with the OS controlling the memory allocation area, type, and segment registers, and loading the program in any empty memory area.

# (a) Before relocation

# (b) After relocation

# 3.5 Effective Address

The effective address (EA) is an unsigned 16-bit number and is the memory address to be processed by an instruction represented by the offset value for the base address of the corresponding segment. This is calculated by the execution unit (EXU) according to the specification of an instruction operand.

The EXU calculates EA in several different methods (addressing mode). The method is selected by the 2nd byte operand of the instruction. The information encoded in the 2nd byte of the instruction indicates how the effective address of the memory indicated by the operand is calculated by the EXU. This operand code is automatically generated by a compiler or assembler from a program statement or instruction description. All addressing modes are available in assembly language.

The method of calculation of EA is shown below. Figure 3-10 indicates that the EXU calculates EA by adding the displacement, base register contents, and index register contents. For any instruction, these three elements can be combined arbitrarily. The displacement is an 8-bit or 16-bit immediate number indicated by an operand.

Figure 3-10. Memory Address Calculation

# 3.6 Instruction Set

# 3.6.1 List of instruction sets by function

The V30MX instructions consist of 101 instructions in its instruction set and functionally these are roughly classified into the following 27 kinds.

Refer to the **16-Bit V Series User's Manual – Instruction** for details of each instruction. The number of clocks is shown in **APPENDIX LIST OF NUMBER OF INSTRUCTION EXECUTION CLOCKS.**

| Instruction Group                    | Mnemonic                                                                                                                 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Data transfer instruction            | LDEA, MOV, TRANS, TRANSB, XCH                                                                                            |

| Repeat prefix                        | REP, REPC, REPE, REPNC, REPNE, REPNZ, REPZ                                                                               |

| Primitive block transfer instruction | CMPBK, CMPBKB, CMPBKW, CMPM, CMPMB, CMPMW, LDM, LDMB, LDMW, MOVBK, MOVBKB, MOVBKW, STM, STMB, STMW                       |

| Bit field manipulation instruction   | EXT, INS                                                                                                                 |

| Input/output instruction             | IN, OUT                                                                                                                  |

| Primitive input/output instruction   | INM, OUTM                                                                                                                |

| Addition/subtraction instruction     | ADD, ADDC, SUB, SUBC                                                                                                     |

| BCD operation instruction            | ADD4S, CMP4S, ROL4, ROR4, SUB4S                                                                                          |

| Increment/decrement instruction      | DEC, INC                                                                                                                 |

| Multiplication instruction           | MUL, MULU                                                                                                                |

| Division instruction                 | DIV, DIVU                                                                                                                |

| BCD adjustment instruction           | ADJ4A, ADJ4S, ADJBA, ADJBS                                                                                               |