8000 Series Components Manual

The information in this document is subject to change without notice and should not be construed as a commitment by Tundra Semiconductor Corporation. While reasonable precautions have been taken, Tundra Semiconductor Corporation assumes no responsibility for any errors that may appear in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Tundra Semiconductor Corporation.

The acceptance of this document will be construed as an acceptance of the foregoing conditions.

Tundra Semiconductor Corporation: formerly Newbridge Microsystems.

8000 Series Components Manual

© Copyright 1996, Tundra Semiconductor Corporation

All Rights Reserved

Document: 9000000.MD302.01

Printed in Canada

# **Corporate Profile**

Tundra Semiconductor Corporation is a privately-held, international, fabless semiconductor company focused on the design, development and delivery of bus-bridging components for embedded systems. Previously Newbridge Microsystems, a division of Newbridge Networks Corporation, Tundra commenced operations under its new name on December 18, 1995.

Our mission statement is simple: We at Tundra are committed to providing high-quality components that enable embedded systems designers to get to market faster with a more competitive product. Tundra takes a 'total product solution' approach to new products, with evaluation boards, executable models, device drivers, application notes, and manuals, in addition to our acclaimed applications engineering support.

Tundra offers a well accepted and expanding family of VMEbus bus-bridging components, plus a growing line of embedded PCI bus-bridging chips that support processors such as the Motorola® 68K and QUICC<sup>TM</sup> and PowerQUICC<sup>TM</sup> lines.

In addition, we offer a family of DES (Data Encryption Standard) -based encryption chips as well as a line of industry-standard 8000 Series peripheral IC's.

#### HEADQUARTERS

603 MARCH RD KANATA, ON K2K 2M5 CANADA Tel: 613-592-0714 Fax: 613-592-1320

or from within North America Tel: 1-800-267-7231

Visit our website at: www.tundra.com Email: support@tundra.com

iv

**Table of Contents**

| 1 | Produ   | ct Index and Ordering 1-1                 |

|---|---------|-------------------------------------------|

|   | 1.1     | How to Order 1-1                          |

|   | 1.2     | Product Listing 1-2                       |

|   | 1.3     | 8000 Series Product Index 1-2             |

|   | 1.4     | Ordering Information and Product Code 1-3 |

|   | 1.5     | Product Cross Reference 1-4               |

|   | 1.6     | Package Codes and Mechanicals 1-6         |

| 2 | 8000 \$ | Series Products                           |

|   | 2.1     | CA80C85B                                  |

|   | 2.2     | CA82C37A                                  |

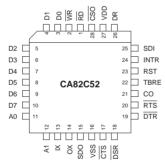

|   | 2.3     | CA82C52                                   |

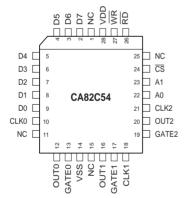

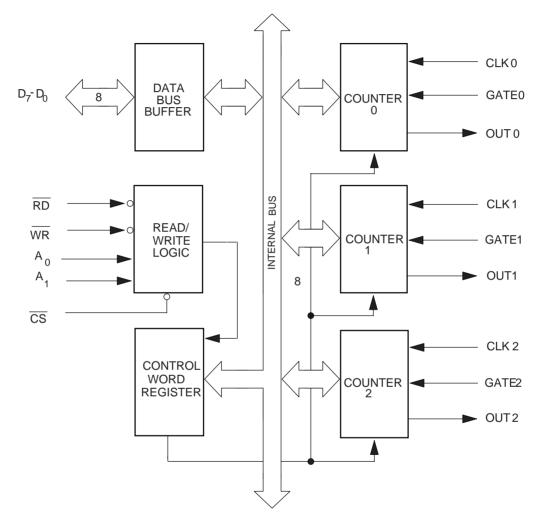

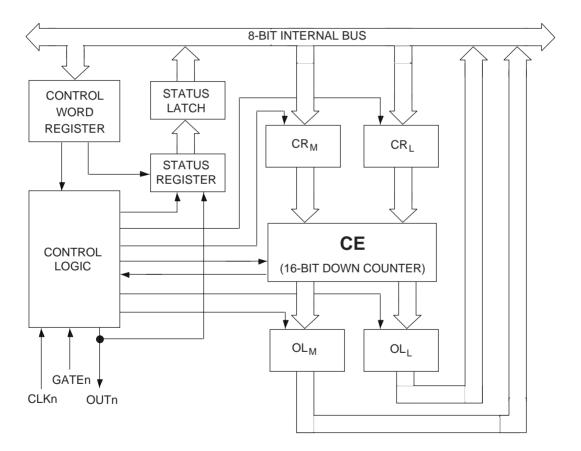

|   | 2.4     | CA82C54                                   |

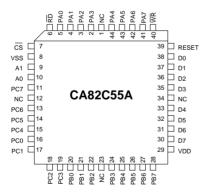

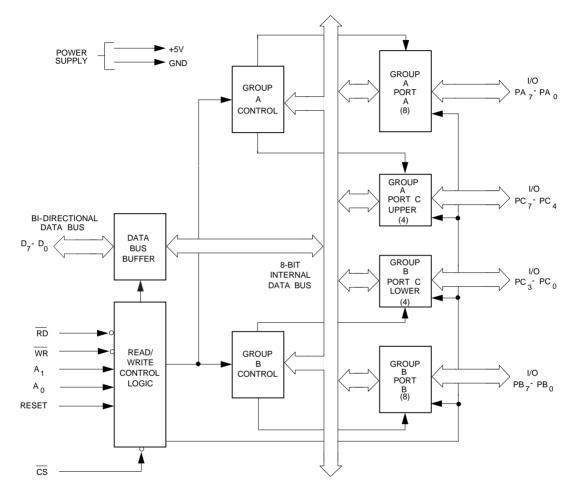

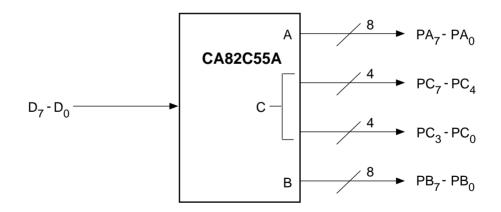

|   | 2.5     | CA82C55A                                  |

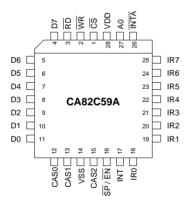

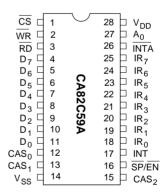

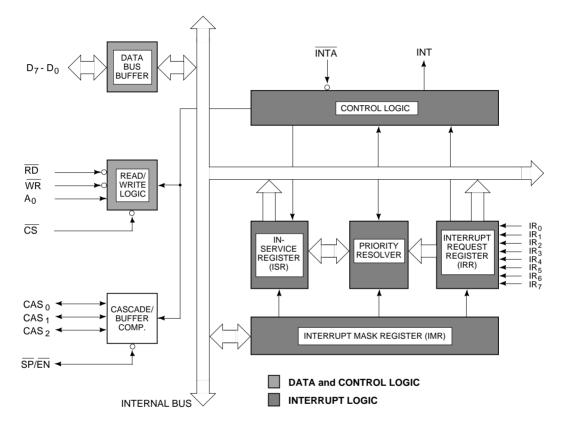

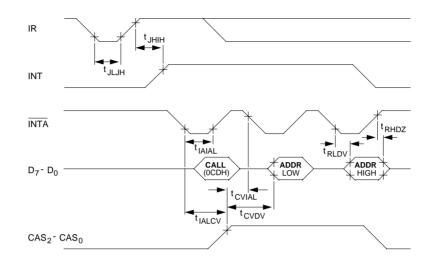

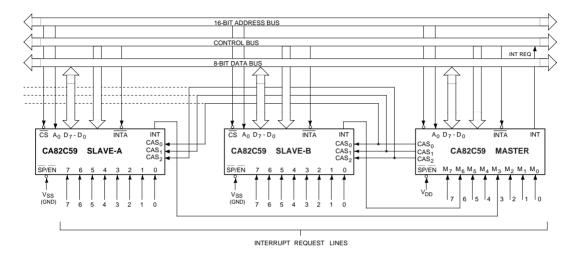

|   | 2.6     | CA82C59A 2-123                            |

| 3 | World   | lwide Sales Network Sales-1               |

# **1 Product Index and Ordering**

# 1.1 How to Order

This chapter is organized into the following sections:

- "Product Listing" on page 1-2, lists our entire 8000 series product family.

- "8000 Series Product Index" on page 1-2, shows you the valid option codes for each of our devices. It also points to related technical and mechanical information for each device.

- "Ordering Information and Product Code" on page 1-3, lists Tundra's packaging, temperature and speed codes.

- "Product Cross Reference" on page 1-4, compares our 8000 series products with similar products of other companies.

- "Package Codes and Mechanicals" on page 1-6, provides a mechanical drawing of each package type.

To use this chapter effectively, determine which of our devices best suits your needs by using the Product Listing on the following page. Then, use the Ordering Information and Product Code tables to help you find the product that matches your system requirements.

If you require any assistance call the nearest Representative, Distributor, or our factory to place an order. (See "Worldwide Sales Network" on page Sales-1.)

# **1.2 Product Listing**

|                     |                                          | Ordering<br>Information<br>Page | Package Codes<br>and Mechanicals<br>Page | Technical<br>Information<br>Page |

|---------------------|------------------------------------------|---------------------------------|------------------------------------------|----------------------------------|

| 8000 Series Product | ts                                       |                                 |                                          |                                  |

| CA80C85B            | High Performance 8-Bit CMOS<br>Processor | 1-1                             | 1-8                                      | 2-1                              |

| CA82C37A            | Programmable DMA Controller              | 1-1                             | 1-8, 1-10                                | 2-17                             |

| CA82C52             | CMOS Serial Controller Interface         | 1-1                             | 1-7, 1-9                                 | 2-45                             |

| CA82C54             | Programmable Interval Timer              | 1-1                             | 1-6, 1-9                                 | 2-69                             |

| CA82C55A            | Programmable Peripheral<br>Interface     | 1-1                             | 1-8, 1-10                                | 2-91                             |

| CA82C59A            | Programmable Interrupt<br>Controller     | 1-1                             | 1-7, 1-9                                 | 2-123                            |

# 1.3 8000 Series Product Index

| Product  | Description                              | Speed          | Temperature<br>Range |    | ge Cod<br>ad Cou |    |

|----------|------------------------------------------|----------------|----------------------|----|------------------|----|

|          |                                          |                | Kange                | Р  | Ν                | М  |

| CA80C85B | High Performance 8-Bit CMOS<br>Processor | 3, 5, 6, 8 MHz | C, I                 | 40 | 44               |    |

| CA82C37A | Programmable DMA Controller              | 5, 8, 10 MHz   | C, I                 | 40 | 44               | —  |

| CA82C52  | CMOS Serial Controller Interface         | 16 MHz         | C, I                 | 28 | 28               | _  |

| CA82C54  | Programmable Interval Timer              | 5, 8, 10 MHz   | C, I                 | 24 | 28               |    |

| CA82C55A | Programmable Peripheral Interface        | 5, 8, 10 MHz   | C, I                 | 40 | 44               | —  |

| CA82C59A | Programmable Interrupt Controller        | 8, 10 MHz      | C, I                 | 28 | 28               | 28 |

Speed, Temperature Range and Package Codes are defined on the next page.

This table shows only the most commonly available package options. Where a package lead count is not given, the device is either not available in that package, or is available by special order only. Please contact the factory directly for more information.

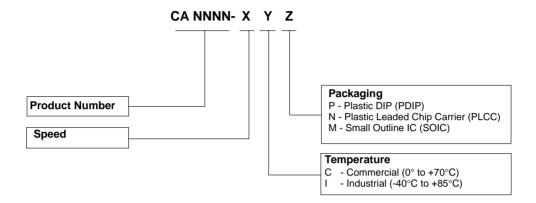

# **1.4 Ordering Information and Product Code**

*Tundra* products are designated by a Product Code. When ordering, refer to products by their full code. For unusual, and/or specific packaging or processing requirements not covered by the standard product line, please contact our factory directly.

Note that all products are not necessarily available in all packages.

# 1.5 **Product Cross Reference**

| Tundra S | emicond                                        | luctor Corp.                            | Intel                                                                     | Harris                                                | Mitsubishi                                                            | I                                      | NEC                                       | OKI                                                               |

|----------|------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------|-------------------------------------------|-------------------------------------------------------------------|

|          |                                                |                                         |                                                                           |                                                       |                                                                       | New Line                               | Former Line                               |                                                                   |

| CA80C85B | -3CP<br>-5CP<br>-6CP                           | High<br>Performance<br>8-Bit CMOS       | —<br>P8085AH-2<br>P8085H-1                                                |                                                       | <br>M5M80C85AP-2<br>                                                  |                                        | <br>μPD8085AC-2,<br>μPD8085AHC-2<br>      |                                                                   |

|          | -8CP<br>-8CN                                   | Processor                               | _                                                                         | _                                                     | _                                                                     | _                                      | _                                         | _                                                                 |

| CA82C37A | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable<br>DMA Controller          | P8237A, P8237A-4,<br>P8237A-5, P82C37A-5<br>—<br>—<br>—<br>—<br>—<br>—    | CP82C37A-5<br>CS82C37A-5<br>CP82C37A<br>CS82C37A<br>— | M5M82C37AP-5<br>—<br>—<br>—<br>—<br>—<br>—                            | <br><br>μPD71037C<br>μPD71037L         | <br><br>μPD8237AC-5<br>                   | MSM82C37A-5RS<br>MSM82C37A-5JS<br>—<br>—<br>—<br>—<br>—<br>—<br>— |

| CA82C52  | -16CP<br>-16CN                                 | CMOS Serial<br>Controller<br>Interface  |                                                                           | CP82C52<br>CS82C52                                    | —                                                                     | —                                      | —                                         | _                                                                 |

| CA82C54  | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable<br>Interval Timer          |                                                                           | <br>CP82C54<br>CS82C54<br>                            | <br>M5M82C54P<br><br>                                                 | <br><br>μPD71054<br><br>               | <br>μPD8253AC-2<br><br>                   | <br>MSM82C53-5RS<br><br>MSM82C54-2RS<br>MSM82C54-2JS              |

| CA82C55A | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable<br>Peripheral<br>Interface | P8255, P8255-5<br>N8255, N8255-5<br>P82C551-2<br>N82C55A-2<br>—<br>—<br>— | CP82C55A-5<br>—<br>CS82C55A<br>—<br>—                 | M5L8255AP-5,<br>M5M82C55AP-5<br>—<br>M5M82C55AP-2<br>—<br>—<br>—<br>— | μPD71055<br>—<br>—<br>—<br>—<br>—<br>— | μPD8255AC-2<br>—<br>—<br>—<br>—<br>—<br>— | MSM82C55A-5RS<br>                                                 |

| CA82C59A | -8CP<br>-8CN<br>-10CP<br>-10CN<br>-10CM        | Programmable<br>Interrupt<br>Controller | P8259-2, P82C59A-2<br>N8259-2<br><br><br><br>                             | CP82C59A<br>CS82C59A<br>—<br>—<br>—                   | M5M82C59AP-2<br>—<br>—<br>—<br>—                                      |                                        |                                           | MSM82C59A-2RS<br>MSM82C59A-2JS<br>—<br>—<br>—<br>—                |

| Tundra   | Semico                                         | nductor Corp.                               | AMD                                                                      | Samsung                                                             | Toshiba                                     | UMC                                                       |

|----------|------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------|

| CA80C85B | -3CP<br>-5CP<br>-6CP<br>-8CP<br>-8CN           | High Performance<br>8-Bit CMOS<br>Processor |                                                                          |                                                                     |                                             | <br>                                                      |

| CA82C37A | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable DMA<br>Controller              | P8237A-5<br>—<br>—<br>—<br>—<br>—<br>—                                   | —<br>—<br>—<br>KS82C37A-10CP<br>KS82C37A-10CL                       |                                             | UM8237A-4<br>UM8237A-5<br>—<br>—<br>—<br>—<br>—<br>—<br>— |

| CA82C52  | -16CP<br>-16CN                                 | CMOS Serial<br>Controller Interface         | —                                                                        | KS82C52-16CP<br>KS82C52-16CL                                        | _                                           | _                                                         |

| CA82C54  | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable<br>Interval Timer              |                                                                          | —<br>KS82C54-8CP<br>KS82C54-8CL<br>KS82C54-10CP<br>KS82C54-10CL     |                                             | —<br>—<br>UM8254<br>UM8254-2                              |

| CA82C55A | -5CP<br>-5CN<br>-8CP<br>-8CN<br>-10CP<br>-10CN | Programmable<br>Peripheral Interface        | 2.5 MHz or<br>3.3 MHz Only<br>CS82C55A-5<br>CP82C55A<br>—<br>—<br>—<br>— | —<br>KS82C55A-8CP<br>KS82C55A-8CL<br>KS82C55A-10CP<br>KS82C55A-10CL |                                             | <br><br><br>                                              |

| CA82C59A | -8CP<br>-8CN<br>-10CP<br>-10CN<br>-10CM        | Programmable<br>Interrupt Controller        | P8259A-2, P82C59A-2<br>N8259A-2, N82C59A-2<br>—<br>—<br>—<br>—           | —<br>—<br>KS82C59A-10CP<br>KS82C59A-10CL<br>—                       | TMP82C59AP-2<br>—<br>—<br>—<br>TMP82C59AM-2 | UM8259A<br>—<br>—<br>—<br>—<br>—                          |

| These products no longer supported |

|------------------------------------|

| by their original manufacturers.   |

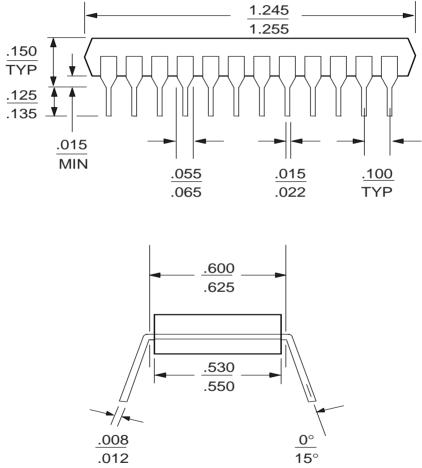

# **1.6** Package Codes and Mechanicals

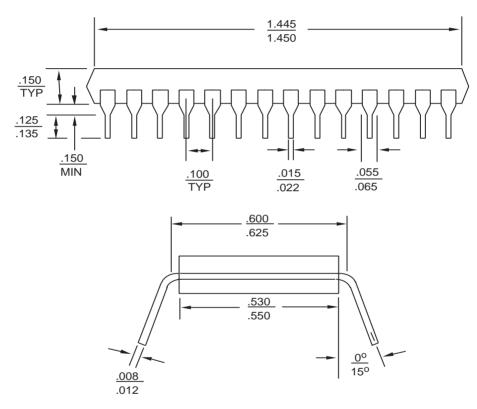

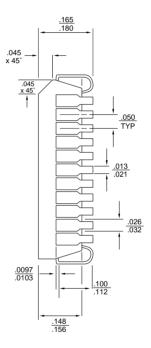

# **1.6.1 PDIP** (Package Code: P)

24 - pin PDIP

All dimensions in inches.

Note: This package conforms to JEDEC reference MS-011, Variation AA.

# 28 - pin PDIP

All dimensions in inches

Note: This package conforms to JEDEC reference MS-011, Variation AB.

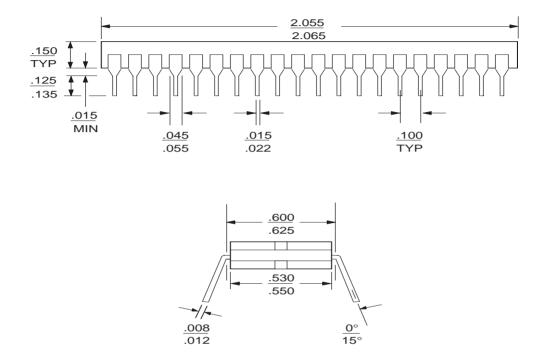

## 40 - pin PDIP

All dimensions in inches

Note: This package conforms to JEDEC reference MS-011, Variation AC.

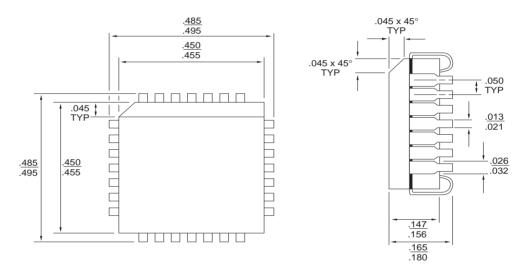

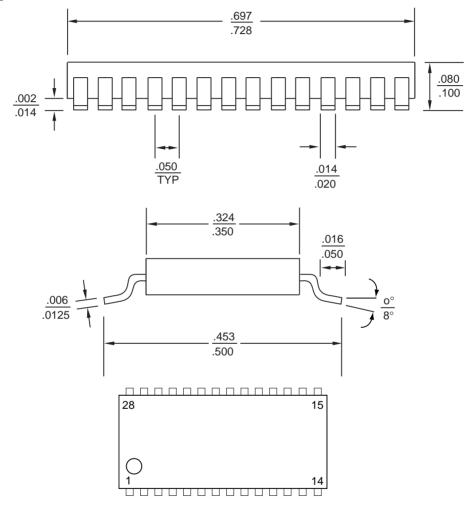

# 1.6.2 PLCC (Package Code: N)

28 - pin PLCC

All dimensions in inches.

Note: This package conforms to JEDEC reference MS-018, Variation AB.

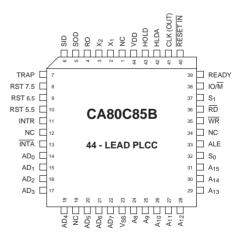

# 44 - pin PLCC

All dimensions in inches.

Note: This package conforms to JEDEC reference MS-018, Variation AC.

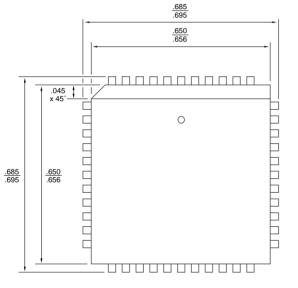

# 1.6.3 SOIC (Package Code: M)

28 - pin SOIC

All dimensions in inches

Note: This package conforms to JEDEC reference MO-059, Variation AC.

# 8000 Series Products

2

3

# **Worldwide Sales Network**

# CA80C85B HIGH PERFORMANCE 8-BIT CMOS MICROPROCESSOR

- Enhanced, high performance CA80C85B microprocessor features pin and functional compatibility with industry standard 8085 and 8085A

- Very low power consumption achieved with proven CMOS implementation

- TTL compatible input/output voltages

- Fast Available in 8 MHz, 6 MHz, 5 MHz and 3 MHz speed versions

- Full support of extended instruction set, and standard 8080 and 8085/8085A instruction sets

- Runs over 10,000 CP/M<sup>®</sup> programs

- On-chip clock generator (using external crystal, LC or RC network)

- · Direct addressing to 64K bytes

- Four Interrupt inputs (one non-maskable)

- One of the multi-sourced, Calmos<sup>™</sup> 8000 series products

The CA80C85B is an 8-bit microprocessor having complete pin and functional compatibility with industry standard 8085s and 8085As. In addition, it supports the special 8085 extended instruction set. The CA80C85B includes an onboard system controller, clock generator, serial I/O port and direct addressing capability to 64K bytes of memory. The device also utilizes a multiplexed data bus, with 16-bit addresses split between an 8-bit address bus and an 8-bit data bus.

The CA80C85B is manufactured in CMOS and supplied in a PDIP package configuration suitable for commercial and industrial applications.

The CA80C85B provides the systems designer with single component CPU functionality, thereby reducing the parts count. Its low power consumption and TTL I/O compatibility make the CA80C85B particularly well suited to portable or standby type applications.

| $X_1$<br>$X_2$<br>RO<br>SOD<br>TRAP<br>RST 7.5<br>RST 6.5<br>RST 5.5<br>INTR<br>AD <sub>0</sub><br>AD <sub>1</sub><br>AD <sub>2</sub><br>AD <sub>3</sub><br>AD <sub>4</sub><br>AD <sub>5</sub><br>AD <sub>6</sub><br>AD <sub>7</sub> | 1       2       3       4       5       6       7       8       10       11       12       13       14       15       16       17       18       20 | CA80C85B | 40<br>39<br>38<br>37<br>36<br>35<br>34<br>33<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22<br>22<br>21 |   | $\begin{array}{c} V \ DD \\ HOLD \\ HOLD \\ LLA \\ CLK \ (OUT) \\ RESETIN \\ READY \\ IO \ / M \\ S1 \\ RD \\ WR \\ ALE \\ S0 \\ A15 \\ A15 \\ A14 \\ A10 \\ A11 \\ A10 \\ A9 \\ \end{array}$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v <sub>ss</sub>                                                                                                                                                                                                                      | Ц <u>20</u>                                                                                                                                         |          | 21                                                                                                                         | _ | A <sub>8</sub>                                                                                                                                                                                |

Figure 2-1: PDIP Pin Configurations

Figure 2-2: PLCC Pin Configurations

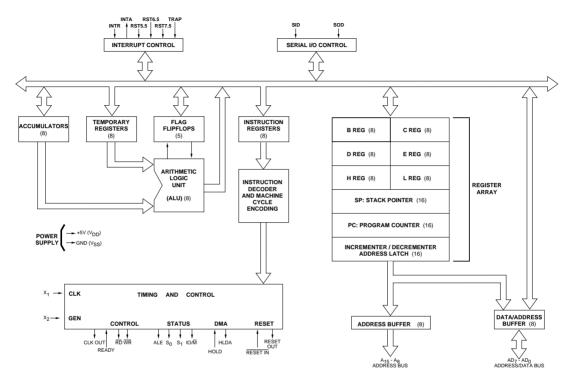

Figure 2-3: CA80C85B Block Diagram

#### Table 2-1: Pin Descriptions

| Symbol<br>PDIP                    | Pin        | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A <sub>8</sub> - A <sub>15</sub>  | 21 - 28    | 0    | High Address Bus: the most significant 8 bits of the memory address.                                                                                                                                                                                                                                                                                                                  |  |  |

| AD <sub>0</sub> - AD <sub>7</sub> | 12 - 19    | I/O  | Low Address and Data Bus: the least significant 8 bits of the memory address multiplexed with an 8-bit data bus.                                                                                                                                                                                                                                                                      |  |  |

| ALE                               | 30         | 0    | Address Latch Enable Out: This signal occurs during the first clock state of a machine cycle. The falling edge of the ALE may be used to strobe the status information.                                                                                                                                                                                                               |  |  |

| CLK                               | 37         | 0    | <b>Clock</b> : This signal can be used as a system clock. The period of CLK is twice the period of the $X_1, X_2$ input.                                                                                                                                                                                                                                                              |  |  |

| HLDA                              | 38         | 0    | Hold Acknowledge: Indicates that the CPU has received the HOLD request and that the bus will be relinquished in the next clock cycle.                                                                                                                                                                                                                                                 |  |  |

| HOLD                              | 39         | I    | <b>Hold Request</b> : Is used to indicate that another master is requesting the use of the address and data buses. When HOLD is acknowledged (HLDA), the Address, Data, $\overline{\mathtt{ND}}$ , $\overline{\mathtt{WR}}$ and $IO/\overline{\mathtt{M}}$ lines are set to the high impedance state. Note that the CPU can regain control of the bus only after the HOLD is removed. |  |  |

| INTA                              | 11         | 0    | <b>Interrupt Acknowledge</b> : This active low signal indicates that the interrupt request input (INTR) has been recognized and acknowledged.                                                                                                                                                                                                                                         |  |  |

| INTR                              | 10         | о    | <b>Interrupt Request</b> : This is a general purpose interrupt. When INTR goes HIGH, it will inhibit the Program Counter, generate an interrupt acknowledge ( $\overline{INTA}$ ) signal, and sample the data bus for a RESTART or CALL instruction.                                                                                                                                  |  |  |

| IO/M                              | 34         | 0    | Machine Cycle Status: See $S_0$ and $S_1$ status bits for further details.                                                                                                                                                                                                                                                                                                            |  |  |

| RD                                | 32         | 0    | <b>Read Control</b> : Active low signal is used to indicate that selected memory or I/O device is to be read with the data bus available for the data transfer. $\overline{RD}$ is set to a high impedance state during HOLD, HALT and RESET modes.                                                                                                                                   |  |  |

| READY                             | 35         | I    | <b>Ready</b> : This signal is set to HIGH during read or write cycles to indicate that the selected memory or I/O device is ready to send or receive data.                                                                                                                                                                                                                            |  |  |

| RESET IN                          | 36         | I    | <b>Reset In</b> : Active low signal sets the Program Counter to zero, and resets the interrupt enable (INTE) and HLDA flipflop. Note that so long as RESETIN is held low, the CPU is held in a reset condition.                                                                                                                                                                       |  |  |

| RO                                | 3          | 0    | Reset Out: Indicates that the CPU is being reset. This signal can be used as a system RESET.                                                                                                                                                                                                                                                                                          |  |  |

| RST7.5<br>RST6.5<br>RST5.5        | 7, 8, 9    | I    | <b>Restart Interrupts</b> : These inputs provide three maskable interrupts which invoke an automatic internal restart. RST7.5 is the highest relative priority, followed by RST6.5 and RST5.5. All three interrupts have a higher priority than INTR.                                                                                                                                 |  |  |

| $S_0 - S_1$<br>IO/ $\overline{M}$ | 29, 33, 34 | 0    | <b>Status Outputs</b> : These signals provide an indication of the machine status during any given cycle. All become valid at the beginning of a machine cycle, and remain stable for the duration of that cycle. The status may be latched by the falling edge of the ALE signal.                                                                                                    |  |  |

| SID                               | 5          | I    | Serial Input Data: Data on SID is loaded into accumulator bit 7 when a RIM instruction is executed.                                                                                                                                                                                                                                                                                   |  |  |

| SOD                               | 4          | 0    | Serial Output Data: This signal is set or reset by the SIM instruction.                                                                                                                                                                                                                                                                                                               |  |  |

| TRAP                              | 6          | I    | <b>Trap Interrupt</b> : Is a non-maskable restart interrupt. It is the highest priority interrupt, and is unaffected by an interrupt enable (INTE).                                                                                                                                                                                                                                   |  |  |

| V <sub>DD</sub>                   | 40         | -    | Power: +5V supply                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>SS</sub>                   | 20         | -    | Ground: Ground reference.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| WR                                | 31         | о    | Write Control: This active low signal is used to indicate that selected memory or I/O device is to be written to, with the data bus available for the data transfer. WR is set to a high impedance state during HOLD, HALT, and RESET modes.                                                                                                                                          |  |  |

| X <sub>1</sub> , X <sub>2</sub>   | 1,2        | I    | $X_1$ , $X_2$ : These two inputs are connected to clock source which is used to drive the internal clock generator. The clock source may be a crystal, LC or RC network. An external clock cal also be connected directly to $X_1$ , to produce an internal processor clock frequency of one half of the input frequency.                                                             |  |  |

#### FUNCTIONAL DESIGN

The CA80C85B utilizes a stack architecture to enable any part of the external memory to be employed as a Last In/First Out (LIFO) memory stack. A 16-bit stack pointer controls the addressing of this stack. The arrangement allows extensive subroutine nesting and multiple level interrupts to be handled without losing the system status. In addition, the device accepts serial input data and provides serial output data, functions which are controlled by the interrupt mask instructions.

The CA80C85B provides 16-bit arithmetic operation with immediate operators and decimal capability. An 8-bit accumulator, four user accessible flag bits, an 8-bit parallel binary arithmetic unit and six 8-bit data registers, all shown in the block diagram of Figure 2-3, are also provided. CA80C85B timing signals are supplied by an internal clock generator (which can be used with either crystal or RC timing circuits), or by an external clock input signal. Status outputs convey memory I/O instruction and Read/Write timing indications.

For typical, single function type configurations, the CA80C85B is supplied in a 40-pin package, the low pin count a result of multiplexing the Address and Data Bus lines. Pin functions are described in Table 2-1, with the 40-pin DIP pin configuration illustrated in Figure 2-1. The lower processor pin count of this device can be reflected throughout a system design by similar pin count reductions in peripheral chips. Further, this optimization can be achieved without incurring complex or critical timing problems.

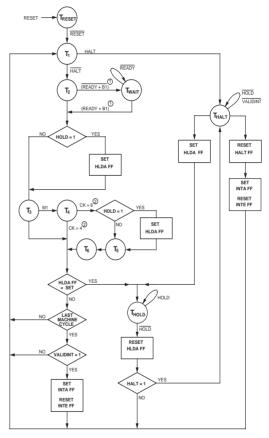

The CA80C85B has five levels of interrupts, including three maskable restart interrupts, one non-maskable TRAP interrupt and a bus vectored interrupt, INTR. Bus control is provided by the  $\overline{RD}$ ,  $\overline{WR}$ ,  $S_0$ ,  $S_1$ , IO/ $\overline{M}$  and  $\overline{INTA}$  interrupt acknowledge signals. When a HOLD control input signal is received, both Address and Data Bus are set to a high-impedance state, and an HLDA output signal acknowledges that microprocessor operation is stopped, and that the buses are available for use by other devices. Note that HOLD and all other interrupt signals are synchronized with the processor's internal clock. This is illustrated in the processor state transition diagram of Figure 2-4.

In addition to the Data Bus, a simple serial interface is provided by the Serial Input Data (SID) and Serial Output Data (SOD) lines. At the software level, the CA80C85B supports the full extended instruction set, offering 10 additional instructions for the production of more efficient code. The five existing condition code flags have also been enhanced with two additional flag bits, one of which indicates a 2s complement overflow.

2. *CK* indicates the number of clock cycles in this machine cycle.

Figure 2-4: State Transition Diagram

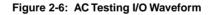

#### Table 2-2: 3 MHz AC Characteristics

## $T_A = -40^{\circ}$ to +85°C, $V_{DD} = +5v + 10\%$ , $t_{CYC} = 320$ ns, $C_L = 150$ pF

| Symbol            | Parameter                                                                   | Limits |      | Units |

|-------------------|-----------------------------------------------------------------------------|--------|------|-------|

| Symbol            | Falameter                                                                   | Min    | Max  |       |

| t <sub>1</sub>    | CLK Low Time                                                                | 80     | -    | ns    |

| t <sub>2</sub>    | CLK High Time                                                               | 120    | -    | ns    |

| t <sub>AC</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control (Note 1)  | 270    | -    | ns    |

| t <sub>ACL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control            | 240    | -    | ns    |

| t <sub>AD</sub>   | A0 - A15 Valid to Valid Data In                                             | -      | 575  | ns    |

| t <sub>AFR</sub>  | Address Float After Leading Edge of RD, INTA                                | -      | 0    | ns    |

| t <sub>AL</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE (Note 1) | 115    | -    | ns    |

| t <sub>ALL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE           | 90     | -    | ns    |

| t <sub>ARY</sub>  | READY Valid from Address Valid                                              | -      | 220  | ns    |

| t <sub>CA</sub>   | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control             | 120    | -    | ns    |

| t <sub>cc</sub>   | Width of Control Low (RD, WR, INTA)                                         | 400    | -    | ns    |

| t <sub>CL</sub>   | Trailing Edge of Control to Leading Edge of ALE                             | 50     | -    | ns    |

| t <sub>CYC</sub>  | CLK Cycle Period                                                            | 320    | 2000 | ns    |

| t <sub>DW</sub>   | Data Valid to Trailing Edge of WR                                           | 420    | -    | ns    |

| t <sub>f</sub>    | CLK Fall Time                                                               | -      | 30   | ns    |

| t <sub>HABE</sub> | HLDA to Bus Enable                                                          | -      | 210  | ns    |

| t <sub>HABF</sub> | Bus Float After HLDA                                                        | -      | 210  | ns    |

| t <sub>HACK</sub> | HLDA Valid to Trailing Edge of CLK                                          | 110    | -    | ns    |

| t <sub>HDH</sub>  | HOLD Hold Time                                                              | 0      | -    | ns    |

| t <sub>HDS</sub>  | HOLD Setup Time to Trailing Edge of CLK                                     | 170    | -    | ns    |

| t <sub>INH</sub>  | INTR Hold Time                                                              | 0      | -    | ns    |

| t <sub>INS</sub>  | INTR RST and TRAP Setup Time to Falling Edge of CLK                         | 160    | -    | ns    |

| t <sub>LA</sub>   | Address Hold Time After ALE                                                 | 100    | -    | ns    |

| t <sub>LC</sub>   | Trailing Edge of ALE to Leading Edge of Control                             | 130    | -    | ns    |

| t <sub>LCK</sub>  | ALE Low During CLK High                                                     | 100    | -    | ns    |

| t <sub>LDR</sub>  | ALE to Valid Data During Read                                               | -      | 460  | ns    |

| t <sub>LDW</sub>  | ALE to Valid Data During Write                                              | -      | 200  | ns    |

| t <sub>11</sub>   | ALE Width                                                                   | 140    | -    | ns    |

| t <sub>IRY</sub>  | ALE to Ready Stable                                                         | -      | 110  | ns    |

| t,                | CLK Rise Time                                                               | -      | 30   | ns    |

| t <sub>RAE</sub>  | Trailing Edge of RD to re-Enabling of Address                               | 150    | -    | ns    |

| t <sub>RD</sub>   | $\overline{RD}$ (or $\overline{INTA}$ ) to Valid Data                       | -      | 300  | ns    |

| t <sub>RDH</sub>  | Data Hold Time After RD, INTA                                               | 0      | -    | ns    |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control                       | 400    | -    | ns    |

| t <sub>RYH</sub>  | READY Hold Time                                                             | 0      | -    | ns    |

| t <sub>RYS</sub>  | READY Setup Time to Leading Edge of CLK                                     | 110    | -    | ns    |

| t <sub>WD</sub>   | Data Valid After Trailing Edge of WR                                        | 100    | -    | ns    |

| t <sub>WDL</sub>  | Leading Edge of WR to Data Valid                                            | -      | 40   | ns    |

| t <sub>XKF</sub>  | X <sub>1</sub> Rising to CLK Falling                                        | 20     | 150  | ns    |

| t <sub>XKR</sub>  | X <sub>1</sub> Rising to CLK Rising                                         | 20     | 120  | ns    |

#### Table 2-3: 5 MHz AC Characteristics

# $T_A = -40^{\circ}$ to +85°C, $V_{DD} = +5v + 10\%$ , $t_{CYC} = 200$ ns, $C_L = 150$ pF

| Symbol            | Parameter                                                                   | Lin | nits | Units |

|-------------------|-----------------------------------------------------------------------------|-----|------|-------|

| Symbol            | Faidilletei                                                                 | Min | Max  |       |

| t <sub>1</sub>    | CLK Low Time                                                                | 40  | -    | ns    |

| t <sub>2</sub>    | CLK High Time                                                               | 70  | -    | ns    |

| t <sub>AC</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control (Note 1)  | 115 | -    | ns    |

| t <sub>ACL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control            | 115 | -    | ns    |

| t <sub>AD</sub>   | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In                     | -   | 330  | ns    |

| t <sub>AFR</sub>  | Address Float After Leading Edge of RD, INTA                                | -   | 0    | ns    |

| t <sub>AL</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE (Note 1) | 50  | -    | ns    |

| t <sub>ALL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE           | 50  | -    | ns    |

| t <sub>ARY</sub>  | READY Valid from Address Valid                                              | -   | 100  | ns    |

| t <sub>CA</sub>   | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control             | 60  | -    | ns    |

| t <sub>cc</sub>   | Width of Control Low (RD, WR, INTA)                                         | 230 | -    | ns    |

| t <sub>CL</sub>   | Trailing Edge of Control to Leading Edge of ALE                             | 25  | -    | ns    |

| t <sub>CYC</sub>  | CLK Cycle Period                                                            | 200 | 2000 | ns    |

| t <sub>DW</sub>   | Data Valid to Trailing Edge of WR                                           | 230 | -    | ns    |

| t <sub>f</sub>    | CLK Fall Time                                                               | -   | 30   | ns    |

| t <sub>HABE</sub> | HLDA to Bus Enable                                                          | -   | 150  | ns    |

| t <sub>HABF</sub> | Bus Float After HLDA                                                        | -   | 150  | ns    |

| t <sub>HACK</sub> | HLDA Valid to Trailing Edge of CLK                                          | 40  | -    | ns    |

| t <sub>HDH</sub>  | HOLD Hold Time                                                              | 0   | -    | ns    |

| t <sub>HDS</sub>  | HOLD Setup Time to Trailing Edge of CLK                                     | 120 | -    | ns    |

| t <sub>INH</sub>  | INTR Hold Time                                                              | 0   | -    | ns    |

| t <sub>INS</sub>  | INTR RST and TRAP Setup Time to Falling Edge of CLK                         | 150 | -    | ns    |

| t <sub>LA</sub>   | Address Hold Time After ALE                                                 | 50  | -    | ns    |

| t <sub>LC</sub>   | Trailing Edge of ALE to Leading Edge of Control                             | 60  | -    | ns    |

| t <sub>LCK</sub>  | ALE Low During CLK High                                                     | 50  | -    | ns    |

| t <sub>LDR</sub>  | ALE to Valid Data During Read                                               | -   | 250  | ns    |

| t <sub>LDW</sub>  | ALE to Valid Data During Write                                              | -   | 140  | ns    |

| t <sub>LL</sub>   | ALE Width                                                                   | 80  | -    | ns    |

| t <sub>LRY</sub>  | ALE to Ready Stable                                                         | -   | 30   | ns    |

| t <sub>r</sub>    | CLK Rise Time                                                               | -   | 30   | ns    |

| t <sub>RAE</sub>  | Trailing Edge of RD to re-Enabling of Address                               | 85  | -    | ns    |

| t <sub>RD</sub>   | RD (or INTA) to Valid Data                                                  | -   | 150  | ns    |

| t <sub>RDH</sub>  | Data Hold Time After RD, INTA                                               | 0   | -    | ns    |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control                       | 220 | -    | ns    |

| t <sub>RYH</sub>  | READY Hold Time                                                             | 0   | -    | ns    |

| t <sub>RYS</sub>  | READY Setup Time to Leading Edge of CLK                                     | 100 | -    | ns    |

| t <sub>WD</sub>   | Data Valid After Trailing Edge of WR                                        | 60  | -    | ns    |

| t <sub>WDL</sub>  | Leading Edge of WR to Data Valid                                            | -   | 20   | ns    |

| t <sub>XKF</sub>  | X <sub>1</sub> Rising to CLK Falling                                        | 20  | 110  | ns    |

| t <sub>XKR</sub>  | X <sub>1</sub> Rising to CLK Rising                                         | 20  | 100  | ns    |

#### Table 2-4: 6 MHz AC Characteristics

## $T_A = -40^{\circ}$ to +85°C, $V_{DD} = +5v + 5\%$ , $t_{CYC} = 167$ ns, $C_L = 150$ pF

| Symbol            | Parameter                                                                   | Lin | Limits | Units |

|-------------------|-----------------------------------------------------------------------------|-----|--------|-------|

| Gymbol            | i aldificter                                                                | Min | Max    |       |

| t <sub>1</sub>    | CLK Low Time                                                                | 34  | -      | ns    |

| t <sub>2</sub>    | CLK High Time                                                               | 59  | -      | ns    |

| t <sub>AC</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control (Note 1)  | 96  | -      | ns    |

| t <sub>ACL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control            | 96  | -      | ns    |

| t <sub>AD</sub>   | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In                     | -   | 292    | ns    |

| t <sub>AFR</sub>  | Address Float After Leading Edge of RD, INTA                                | -   | 0      | ns    |

| t <sub>AL</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE (Note 1) | 42  | -      | ns    |

| t <sub>ALL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE           | 42  | -      | ns    |

| t <sub>ARY</sub>  | READY Valid from Address Valid                                              | -   | 83     | ns    |

| t <sub>CA</sub>   | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control             | 50  | -      | ns    |

| t <sub>cc</sub>   | Width of Control Low (RD, WR, INTA)                                         | 192 | -      | ns    |

| t <sub>CL</sub>   | Trailing Edge of Control to Leading Edge of ALE                             | 20  | -      | ns    |

| t <sub>CYC</sub>  | CLK Cycle Period                                                            | 167 | 2000   | ns    |

| t <sub>DW</sub>   | Data Valid to Trailing Edge of WR                                           | 192 | -      | ns    |

| t <sub>f</sub>    | CLK Fall Time                                                               | -   | 25     | ns    |

| t <sub>HABE</sub> | HLDA to Bus Enable                                                          | -   | 125    | ns    |

| t <sub>HABE</sub> | Bus Float After HLDA                                                        | _   | 125    | ns    |

| t <sub>HACK</sub> | HLDA Valid to Trailing Edge of CLK                                          | 33  | -      | ns    |

| t <sub>HDH</sub>  | HOLD Hold Time                                                              | 0   | -      | ns    |

| t <sub>HDS</sub>  | HOLD Setup Time to Trailing Edge of CLK                                     | 100 | -      | ns    |

| t <sub>INH</sub>  | INTR Hold Time                                                              | 0   | -      | ns    |

| t <sub>INS</sub>  | INTR RST and TRAP Setup Time to Falling Edge of CLK                         | 125 | -      | ns    |

| t <sub>LA</sub>   | Address Hold Time After ALE                                                 | 42  | -      | ns    |

| t <sub>LC</sub>   | Trailing Edge of ALE to Leading Edge of Control                             | 50  | -      | ns    |

| t <sub>LCK</sub>  | ALE Low During CLK High                                                     | 42  | -      | ns    |

| t <sub>LDR</sub>  | ALE to Valid Data During Read                                               |     | 225    | ns    |

| t <sub>LDW</sub>  | ALE to Valid Data During Write                                              | _   | 100    | ns    |

| t <sub>LL</sub>   | ALE Width                                                                   | 67  | _      | ns    |

| t <sub>LRY</sub>  | ALE to Ready Stable                                                         | -   | 25     | ns    |

| tr                | CLK Rise Time                                                               | _   | 25     | ns    |

| t <sub>RAE</sub>  | Trailing Edge of RD to Re-enabling of Address                               | 65  |        | ns    |

| t <sub>RD</sub>   | $\overline{RD}$ (or $\overline{INTA}$ ) to Valid Data                       | -   | 125    | ns    |

| t <sub>RDH</sub>  | Data Hold Time After RD, INTA                                               | 0   | _      | ns    |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control                       | 183 | -      | ns    |

| t <sub>RYH</sub>  | READY Hold Time                                                             | 0   | -      | ns    |

| t <sub>RYS</sub>  | READY Setup Time to Leading Edge of CLK                                     | 84  | -      | ns    |

| t <sub>WD</sub>   | Data Valid After Trailing Edge of $\overline{WR}$                           | 50  | _      | ns    |

|                   | Leading Edge of $\overline{WR}$ to Data Valid                               |     | 16     | ns    |

| t <sub>WDL</sub>  | X <sub>1</sub> Rising to CLK Falling                                        | 20  | 110    | ns    |

| t <sub>XKF</sub>  | A Rising to CER Failing                                                     | 20  | 100    | ns    |

#### Table 2-5: 8 MHz AC Characteristics

# $T_A = -40^{\circ}$ to +85°C, $V_{DD} = +5v + 5\%$ , $t_{CYC} = 125$ ns, $C_L = 150$ pF

| Symbol            | Parameter                                                                   | Lin | nits | Units |

|-------------------|-----------------------------------------------------------------------------|-----|------|-------|

| Symbol            | raiailletei                                                                 | Min | Max  |       |

| t <sub>1</sub>    | CLK Low Time                                                                | 25  | -    | ns    |

| t <sub>2</sub>    | CLK High Time                                                               | 44  | -    | ns    |

| t <sub>AC</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid to Leading Edge of Control (Note 1)  | 72  | -    | ns    |

| t <sub>ACL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid to Leading Edge of Control            | 72  | -    | ns    |

| t <sub>AD</sub>   | A <sub>0</sub> - A <sub>15</sub> Valid to Valid Data In                     | -   | 220  | ns    |

| t <sub>AFR</sub>  | Address Float After Leading Edge of RD, INTA                                | -   | 0    | ns    |

| t <sub>AL</sub>   | A <sub>8</sub> - A <sub>15</sub> Valid Before Trailing Edge of ALE (Note 1) | 31  | -    | ns    |

| t <sub>ALL</sub>  | A <sub>0</sub> - A <sub>7</sub> Valid Before Trailing Edge of ALE           | 31  | -    | ns    |

| t <sub>ARY</sub>  | READY Valid from Address Valid                                              | -   | 63   | ns    |

| t <sub>CA</sub>   | Address (A <sub>8</sub> - A <sub>15</sub> ) Valid After Control             | 37  | -    | ns    |

| t <sub>cc</sub>   | Width of Control Low (RD, WR, INTA)                                         | 144 | -    | ns    |

| t <sub>ci</sub>   | Trailing Edge of Control to Leading Edge of ALE                             | 15  | -    | ns    |

| t <sub>CYC</sub>  | CLK Cycle Period                                                            | 125 | 2000 | ns    |

| t <sub>DW</sub>   | Data Valid to Trailing Edge of WR                                           | 144 | -    | ns    |

| t <sub>f</sub>    | CLK Fall Time                                                               | -   | 25   | ns    |

| t <sub>HABE</sub> | HLDA to Bus Enable                                                          | -   | 94   | ns    |

| t <sub>HABF</sub> | Bus Float After HLDA                                                        | -   | 94   | ns    |

| t <sub>HACK</sub> | HLDA Valid to Trailing Edge of CLK                                          | 25  | -    | ns    |

| t <sub>HDH</sub>  | HOLD Hold Time                                                              | 0   | -    | ns    |

| t <sub>HDS</sub>  | HOLD Setup Time to Trailing Edge of CLK                                     | 78  | -    | ns    |

| t <sub>INH</sub>  | INTR Hold Time                                                              | 0   | -    | ns    |

| t <sub>INS</sub>  | INTR RST and TRAP Setup Time to Falling Edge of CLK                         | 94  | -    | ns    |

| t <sub>IA</sub>   | Address Hold Time After ALE                                                 | 32  | -    | ns    |

| t <sub>LC</sub>   | Trailing Edge of ALE to Leading Edge of Control                             | 38  | -    | ns    |

| t <sub>LCK</sub>  | ALE Low During CLK High                                                     | 32  | -    | ns    |

| t <sub>LDR</sub>  | ALE to Valid Data During Read                                               | -   | 168  | ns    |

| t <sub>LDW</sub>  | ALE to Valid Data During Write                                              | -   | 75   | ns    |

| t <sub>LL</sub>   | ALE Width                                                                   | 50  | -    | ns    |

| t <sub>LRY</sub>  | ALE to Ready Stable                                                         | -   | 25   | ns    |

| tr                | CLK Rise Time                                                               | -   | 25   | ns    |

| t <sub>RAE</sub>  | Trailing Edge of RD to Re-enabling of Address                               | 45  | -    | ns    |

| t <sub>RD</sub>   | RD (or INTA) to Valid Data                                                  | -   | 94   | ns    |

| t <sub>RDH</sub>  | Data Hold Time After RD, INTA                                               | 0   | -    | ns    |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control                       | 138 | -    | ns    |

| t <sub>RYH</sub>  | READY Hold Time                                                             | 0   | -    | ns    |

| t <sub>RYS</sub>  | READY Setup Time to Leading Edge of CLK                                     | 63  | -    | ns    |

| t <sub>WD</sub>   | Data Valid After Trailing Edge of $\overline{WR}$                           | 34  | -    | ns    |

| t <sub>WDL</sub>  | Leading Edge of WR to Data Valid                                            | -   | 16   | ns    |

| t <sub>XKF</sub>  | X <sub>1</sub> Rising to CLK Falling                                        | 20  | 69   | ns    |

| t <sub>XKF</sub>  | X <sub>1</sub> Rising to CLK Rising                                         | 20  | 63   | ns    |

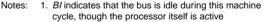

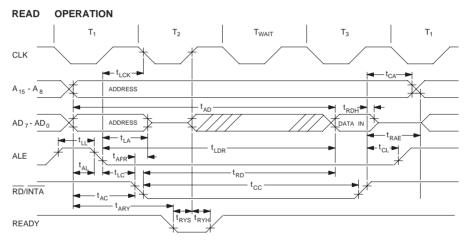

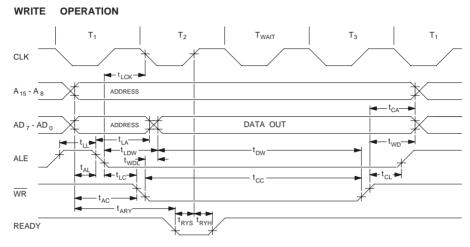

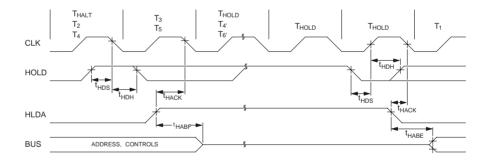

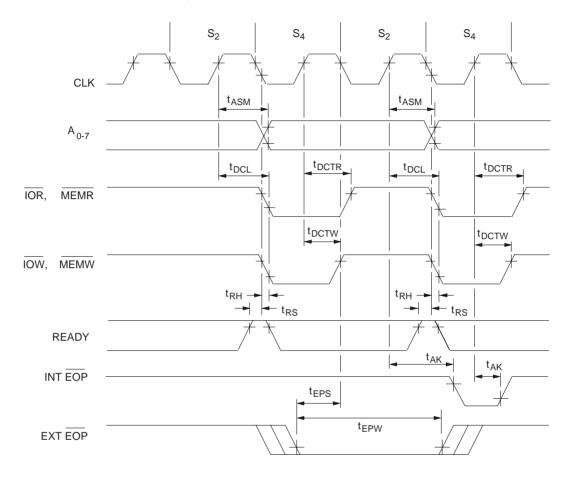

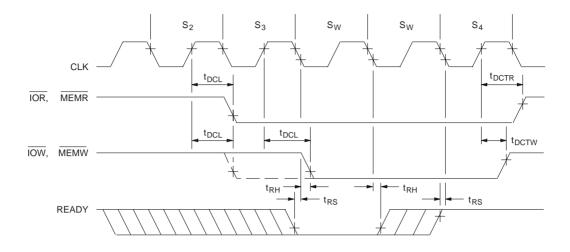

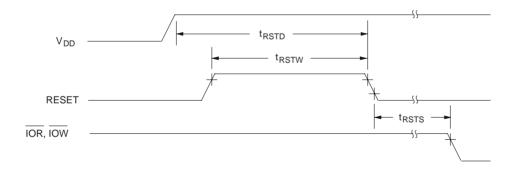

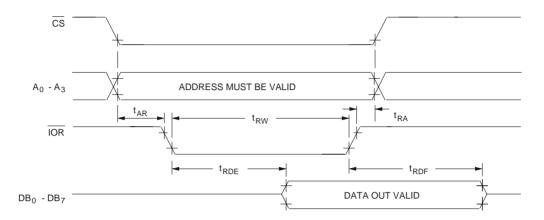

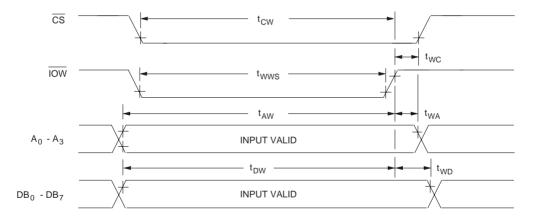

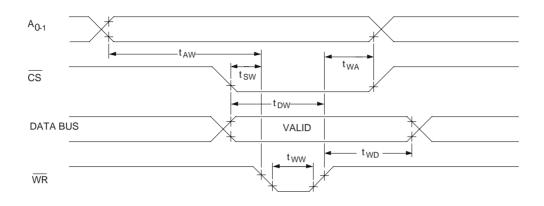

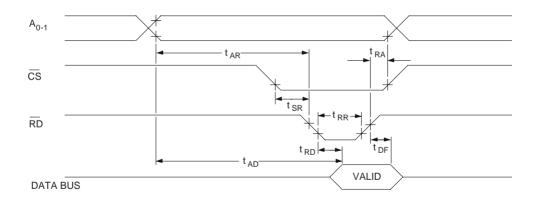

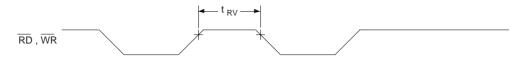

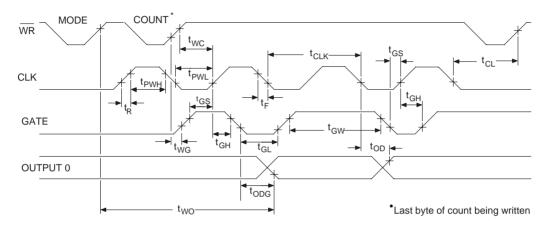

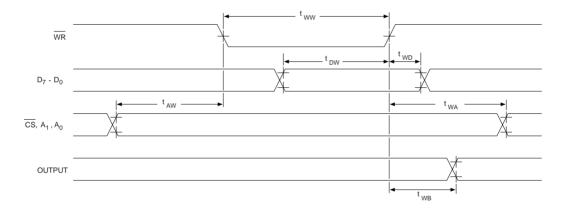

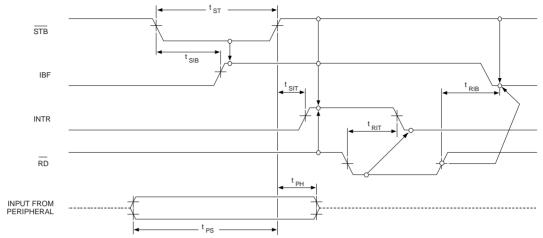

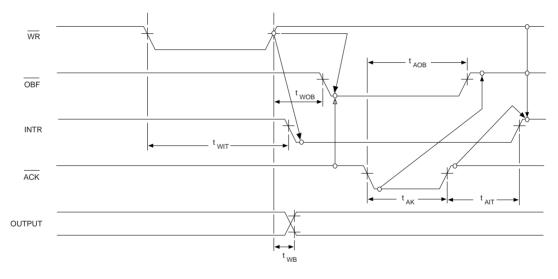

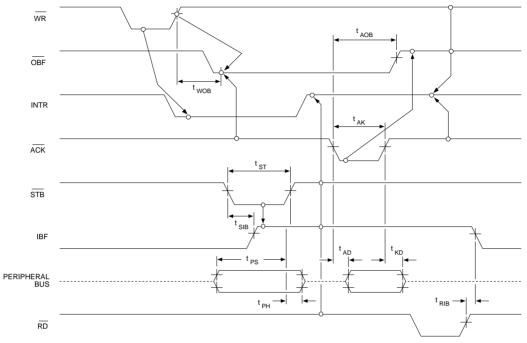

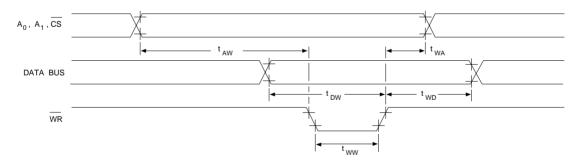

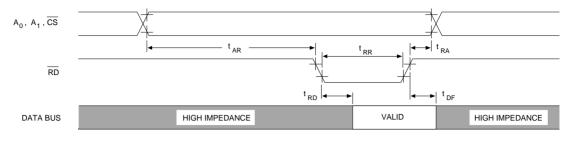

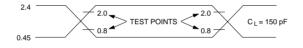

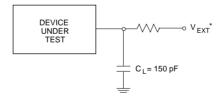

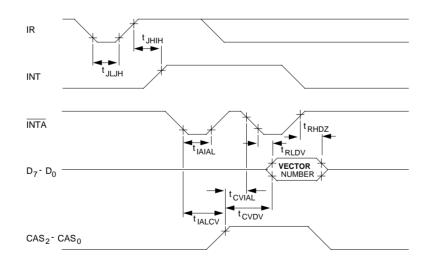

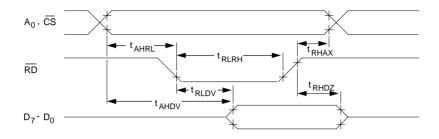

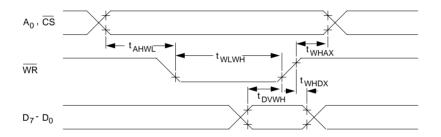

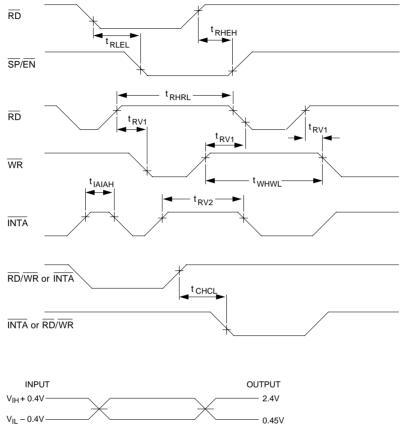

## Figure 2-5: Timing Diagrams

## a) Clock Timing

## b) Read Operation

# Figure 4: Timing Diagrams con't

#### c) Write Operation

## d) Hold Operation

# Figure 4: Timing Diagrams con't

## e) Interrupt Timing

\*NOTE:  $IO/\overline{M}$  is also floating in a high-impedance state during this time

## Table 2-6: DC Characteristics (Commercial and Industrial Temperature Range Devices)

| T <sub>A</sub> = -40° to +85°C, V <sub>DD</sub> = +5v + 10% | t <sub>CYC</sub> = 320 ns (except as noted) |

|-------------------------------------------------------------|---------------------------------------------|

|-------------------------------------------------------------|---------------------------------------------|

| Symbol           | Parameter               | Test Condition                                         | Lir  | Limits               |       |

|------------------|-------------------------|--------------------------------------------------------|------|----------------------|-------|

|                  |                         | Test Condition                                         | Min  | Max                  | Units |

| т                | Derver Surgela Comment  | $t_{CYC} = 320 \text{ ns}, T_A = -40 ^{\circ}\text{C}$ |      | 24                   | mA    |

| I <sub>DD1</sub> | Power Supply Current    | $t_{CYC} = 320 \text{ ns}, T_A = +25 \text{ °C}$       |      | 17                   | mA    |

| T                | Denver Sumply Comment   | $t_{CYC} = 200 \text{ ns}, T_A = -40 \text{ °C}$       |      | 29                   | mA    |

| I <sub>DD2</sub> | Power Supply Current    | $t_{CYC} = 200 \text{ ns}, T_A = +25 ^{\circ}\text{C}$ |      | 21                   | mA    |

| I <sub>IL</sub>  | Input Leakage Current   | $V_{IN} = V_{DD}$ and $V_{IN} = 0$                     | -10  | 10                   | μΑ    |

| I <sub>OL</sub>  | Output Leakage Current  | $0v \le V_{OUT} \le V_{DD}$                            | -10  | 10                   | μΑ    |

| V <sub>HY</sub>  | Hysteresis, RESET       |                                                        | 0.25 |                      | V     |

| V <sub>IH</sub>  | Input High Voltage      |                                                        | 2.2  | V <sub>DD</sub> +0.3 | V     |

| V <sub>IHR</sub> | Input High Level, RESET |                                                        | 2.4  | V <sub>DD</sub> +0.3 | V     |

| VIL              | Input Low Voltage       |                                                        | -0.3 | +0.8                 | V     |

| V <sub>ILR</sub> | Input Low Level, RESET  |                                                        | -0.3 | +0.8                 | V     |

| V <sub>OL</sub>  | Output Low Voltage      | $I_{OL} = 2 \text{ mA}$                                |      | 0.45                 | V     |

| V <sub>OH</sub>  | Output High Voltage     | $I_{OH} = -400 \ \mu A$                                | 2.4  |                      | V     |

|                  |                         | $I_{\text{OH}} = -40 \ \mu\text{A}$                    | 4.2  |                      | V     |

#### Table 2-7: Absolute Maximum Ratings

| Storage Temperature                       | -65°C to +160°C        |

|-------------------------------------------|------------------------|

| Voltage On Any Pin with respect to Ground | -0.3 to VDD +0.3 Volts |

| Output Currents                           | 100mA                  |

| Power Dissipation                         | 1 Watt                 |

| Lead Temperature (Soldering: 10 seconds)  | 300°C                  |

Note: Stresses beyond those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

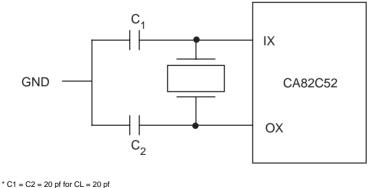

#### **Clock Inputs**

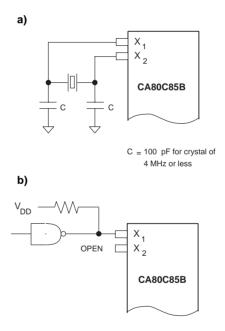

Clock inputs to the CA80C85B are supplied via the two inputs  $X_1$  and  $X_2$ . The  $X_1$  input can be driven either from an external clock, or used with the  $X_2$  input and a crystal to produce an oscillator function. The minimum input

frequency required in both cases is 1 MHz. The actual internal microprocessor clock frequency is one half of the frequency applied or generated externally. For example, a 6 MHz crystal or external clock waveform is required for 3 MHz operation, and a 12 MHz clock source is required for 6 MHz operation.

The  $X_1/X_2$  circuitry is intended to be used with a crystal cut for parallel resonance at the required clock frequency. Such crystals require closely controlled load capacitance in order to resonate at the specified frequency. The CA80C85B has an equivalent parallel capacitance of between 10 and 20 pF. Since most crystals will require higher values of capacitance to resonate at precisely their specified frequency, additional capacitance must be added as shown in Figure 2-6(a).

When the  $X_1$  input is driven from an external clock,  $X_2$  is left open. In this case,  $X_1$  should be driven with a CMOS driver or a TTL device with a pull-up resistor, as shown in Figure 2-6(b). The clock low time must be greater than 80 ns for the 3 MHz device and 30 ns for the 6 MHz.

Figure 2-6: External Clock Circuits

#### Serial I/O

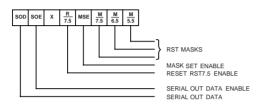

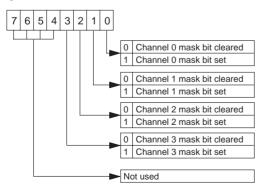

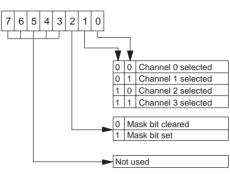

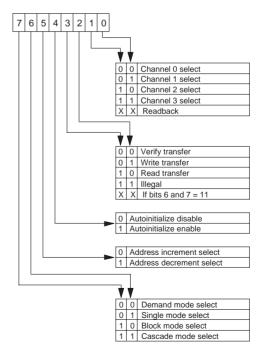

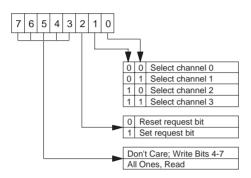

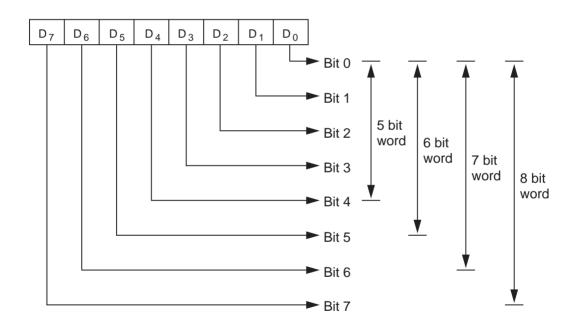

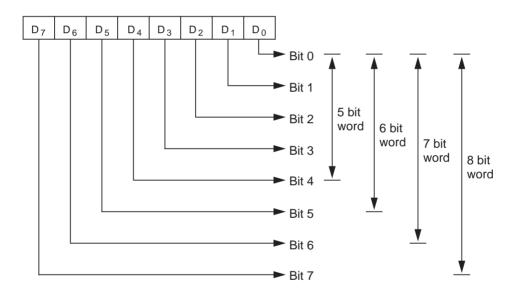

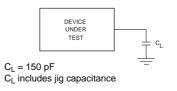

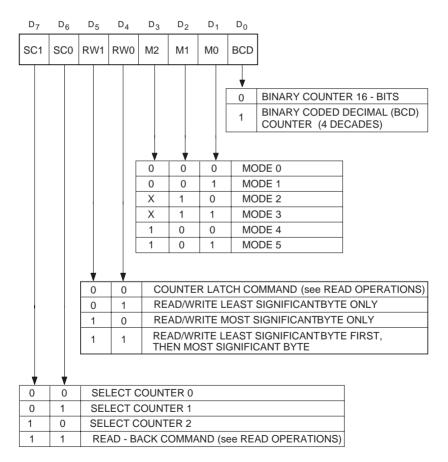

The Set Interrupt Mask (SIM) and Read Interrupt Mask (RIM) instructions provide several functions related to serial port I/O and interrupt mask operations. The SIM instruction is used to output serial data, and to program the interrupt mask register. The output signal, SOD, is set or reset as specified by the SIM instruction, with the accumulator contents constructed as shown in Figure 2-7.

Figure 2-7: SIM Instruction Data Byte

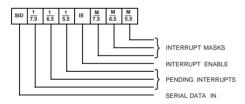

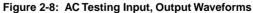

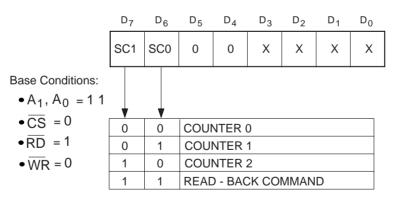

The RIM instruction is used to read the serial input data (SID), as well as the interrupt mask. The accumulator contents after a RIM instruction has been executed are as shown in Figure 2-8.

Figure 2-8: RIM Instruction Data Byte

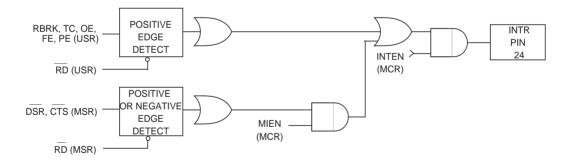

#### Interrupts

The five interrupt levels provided by the CA80C85B are listed by descending order of priority in Table 2-8. TRAP and RSTx.5 are RESTART interrupts. When acknowledged, these four interrupts cause the processor to save the program counter (PC) on the stack, then branch to the restart address specified in the table.

The TRAP interrupt is non-maskable. It is set with a rising edge (low to high) followed by a stable high level until sampled by the processor. To reactivate the TRAP interrupt, the input signal must first go low, then high.

To preserve the status of the Interrupt Enable (IE) flag after a TRAP interrupt has occurred, the interrupt mask must be read and saved immediately after the interrupt has been acknowledged (refer to RIM instruction).

The RST7.5 is a maskable interrupt, set on a rising edge only, and then latched.

The RST6.5 and RST5.5 are maskable interrupts, set with a high level applied to their respective inputs. The status of the three RST interrupt masks can only be affected by the SIM instruction and RESETIM.

The INTR interrupt is also set by a high level applied to the input pin. It is similar in operation to the 8080 INT interrupt in that the action of the processor is dependent on the instruction placed on the bus during the  $\overline{\text{INTA}}$ .

Note that the servicing of any of the five interrupts disables all future interrupts (except TRAPS) until an EI instruction is executed. Of course, an interrupt of higher priority may interrupt a previous interrupt in process if the interrupts have been re-enabled within the interrupt service routine.

#### Table 2-8: Interrupt Restart Address

| Interrupt | Restart Address (HEX)                                                   |

|-----------|-------------------------------------------------------------------------|

| TRAP      | 24H                                                                     |

| RST7.5    | 3CH                                                                     |

| RST6.5    | 34H                                                                     |

| RST5.5    | 2CH                                                                     |

| INTR      | Dependent upon the<br>instruction received on the<br>bus during an INTA |

#### **Status Outputs**

The status of the CA80C85B can be determined from the combination of  $S_0$ ,  $S_1$  and  $IO/\overline{M}$  output signals. These signals are latched on the falling edge of an ALE signal, and are valid while ALE is low. Table 2-9 lists the seven possible types of machine cycles as defined by  $S_0$ ,  $S_1$  and  $IO/\overline{M}$ . Note in the Figure 2-5 timing diagrams that the  $\overline{RD}$  and  $\overline{WR}$  control lines become active after the status signals, when the transfer of data is to take place.

#### Table 2-9: Machine Cycle Status Conditions

| S <sub>0</sub> | S <sub>1</sub> | IO/M | Status                |

|----------------|----------------|------|-----------------------|

| 1              | 0              | 0    | Memory Write          |

| 0              | 1              | 0    | Memory Read           |

| 1              | 0              | 1    | I/O Write             |

| 0              | 1              | 1    | I/O Read              |

| 1              | 1              | 0    | Opcode Fetch          |

| 1              | 1              | 1    | Interrupt Acknowledge |

| Z              | 0              | 0    | Halt                  |

| Z              | Х              | Х    | Hold                  |

| Z              | X              | Х    | Reset                 |

Z - High impedance state

X - Don't care condition

#### **Extended Instructions and Condition Codes**

The CA80C85B Flag Register features two additional condition code flags, for a total of seven. These are illustrated in Figure 2-9. The ten opcodes which comprise the extended instruction set of the CA80C85B microprocessor are described in Table 2-10.

| s | Ζ | UI | AC | 0 | Ρ | V | С | FLAG |

|---|---|----|----|---|---|---|---|------|

| 7 | 6 | 5  | 4  | 3 | 2 | 1 | 0 | BIT  |

V - 2's complement overflow for both 8 and 16-bit arithmetic operations

UI - Underflow indicator (DCX instruction) or Overflow indicator (INX instruction)

$UI = 01 \times 02 + 01 \times R + 02 \times R$

where: 01 = sign of operand 1 02 = sign of operand 2R = sign of result

For subtraction and comparisons, replace 02 with  $\overline{02}$

#### Figure 2-9: Extended Condition Codes

## Table 2-10: CA80C85B Extended Instruction Set

| Name | Opcodes                                                                                | Flags        | Cycles | States  | Description                                                                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------------------------------|--------------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARHL | 00010000<br>Addressing:<br>Register                                                    | СҮ           | 2      | 7       | Arithmetic Shift of H and L to the Right:<br>The contents of registers H and L are shifted right one bit<br>is shifted into the carry bit. The result is saved in registers<br>H and L.<br>H7=H7; Hn-1=Hn; L7=H0; Ln-1=Ln; CY=L0                                                                    |

| DSUB | 00001000<br>Addressing:<br>Register                                                    | Z, S, P, CY, | 3      | 10      | Double Subtraction:<br>The contents of registers B and Care subtracted from the<br>contents of registers H and L. The result is saved in<br>registers H and L.<br>(H) (L)=(H) (L) - (B) (C)                                                                                                         |

| JNUI | 1 1 0 1 1 1 0 1<br>low-order address<br>high-order address<br>Addressing:<br>Immediate | none         | 2 or 3 | 7 or 10 | Jump on NOT UI Flag:<br>Control is transferred to the instruction address specified<br>in bytes 2 and 3 of the current instruction. The result is<br>saved in registers H and L.<br>(H) (L)=(H) (L) - (B) (C)                                                                                       |

| JUI  | 1 1 1 1 1 1 0 1<br>low-order address<br>high-order address<br>Addressing:<br>Immediate | none         | 2 or 3 | 7 or 10 | Jump on UI Flag:<br>Control is transferred to the instruction address specified<br>in bytes 2 and 3 of the current instruction. if the<br>Unsigned Indicator Flag (UI) is set. Otherwise control<br>continues sequentially.<br>(H) (L)=(H) (L) - (B) (C)                                            |

| LDHI | 00101000<br>data<br>Addressing:<br>Immediate Register                                  | none         | 3      | 10      | Load D and E with L Plus Immediate Byte:<br>The immediate byte is added to the contents of<br>registers H and L, and the result is saved in registers<br>D and E.<br>(D) (E) = (H) (L) + (byte 2)                                                                                                   |

| LDSI | 00111000<br>data<br>Addressing:<br>Immediate Register                                  | none         | 3      | 10      | Load D and E with SP Plus Immediate Byte:<br>The 2 bytes of register SP are added to the immediate<br>byte, and the result is saved in registers D and E.<br>(D) (E) = (SPH) (SPL) + (byte 2)                                                                                                       |

| LHLX | 1 1 1 0 1 1 0 1<br>data<br>Addressing:<br>Register Indirect                            | none         | 3      | 10      | Load H and L Indirect Through D and E:<br>The contents of the memory location given by registers D<br>and E are moved to register L. The contents of the next<br>location are moved to register H<br>L=((D) (E)); H=((D)(E) + 1)                                                                    |

| RDEL | 00011000<br>Addressing:<br>Register                                                    | CY, V        | 3      | 10      | Rotate D and E Left Through Carry:<br>The contents of the registers D and E are rotated one bit<br>left through the carry flag. The low-order bit is set equal<br>to the CY flag and the CY flag is set to the value shifted<br>out of the high-order bit<br>Dn+1=Dn; D0; E7; CY=D7; En+1=En; E0=CY |

| RSTV | 11001011<br>Addressing:<br>Register Indirect                                           | none         | 1 or 3 | 6 or 12 | <b>Restart on Overflow:</b><br>If overflow flag V is set, then the actions below are<br>performed. Otherwise, control continues sequentially.<br>If (V): SP - 1=PCH; SP - 2=PCL; SP=SP - 2; PC=40HEX                                                                                                |

| SHLX | 11011001<br>Addressing:                                                                | none         | 3      | 10      | Store H and L Indirect Through D and E:<br>The contents of register L are moved to the memory<br>location given by registers D and E. The contents of<br>register H are                                                                                                                             |

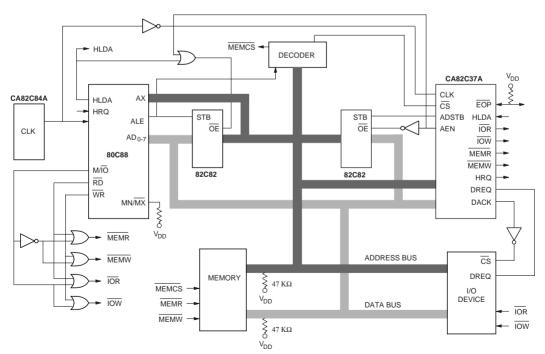

# **CA82C37A** *programmable dma controller*

- Pin and functional compatibility with the industry standard 8237/8237A

- Fully static, high speed 10, 8 and 5 MHz versions available

- Low power CMOS implementation

- TTL input/output compatibility

- Compatible with 8080/85, 8086/88, 80286/386 and 68000 μP families

- · Fully static

- Four independent maskable DMA channels with autoinitialize capability

- · Memory-to-memory transfer

- · Fixed or rotating DMA request priority

- Independent polarity control for DREQ and DACK signals

- · Address increment or decrement selection

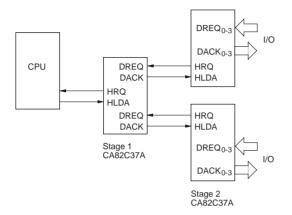

- · Cascadable to any number of channels

The CA82C37A is a high performance, programmable Direct Memory Access (DMA) controller offering pin-forpin functional compatibility with industry standard 8237/8237A. It features four channels, each independently programmable, and is cascadable to any number of channels. Each channel can be programmed to auto-initialize following DMA termination.

In addition, the CA82C37A supports memory-to-memory transfer capability and memory block initialization, as well as a programmable transfer mode.

The CA82C37A is designed to improve system performance by allowing external devices to transfer data directly from the system memory. High speed and very low power consumption make it an ideal component for aerospace and defence applications. The low power consumption also makes it an attractive addition in portable systems, or systems with low power standby modes.

|                   | 1  | $-\bigcirc$ | 40 🗆 A <sub>7</sub>  |

|-------------------|----|-------------|----------------------|

| IOW L             | 2  |             | 39 🗆 A <sub>6</sub>  |

| MEMR              | 3  |             | 38 🗆 A 5             |

| MEMW              | 4  |             | 37 🗆 A 4             |

| NC 🗆              | 5  |             | 36 🗌 EOP             |

| READY             | 6  |             | 35 🗆 A <sub>3</sub>  |

| HLDA 🗆            | 7  | ~           | 34 🗆 A2              |

| ADSTB             | 8  | 5           | 33 🗆 A 1             |

| AEN 🗌             | 9  | A82         | 32 🗆 A <sub>0</sub>  |

| HRQ               | 10 | Ñ           | 31 🗆 V <sub>DD</sub> |

| cs 🗆              | 11 | 0           | 30 🗆 DB 0            |

| CLK 🗆             | 12 | C37 A       | 29 🗖 DB1             |

| RESET             | 13 | 2           | 28 🗆 DB <sub>2</sub> |

| DACK <sub>2</sub> | 14 | -           | 27 🗖 DB3             |

| DACK 3            | 15 |             | 26 🗆 DB4             |

| DREQ3             | 16 |             | 25 DACK0             |

| DREQ <sub>2</sub> | 17 |             | 24 DACK1             |

| DREQ1             | 18 |             | 23 🗆 DB 5            |

| DREQ0             | 19 |             | 22 🗆 DB 6            |

| Vec 🗆             | 20 |             | 21 🗖 DB 7            |

Figure 2-1: PDIP Pin Configurations

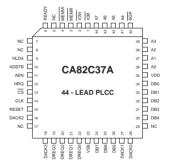

Figure 2-2: PLCC Pin Configurations

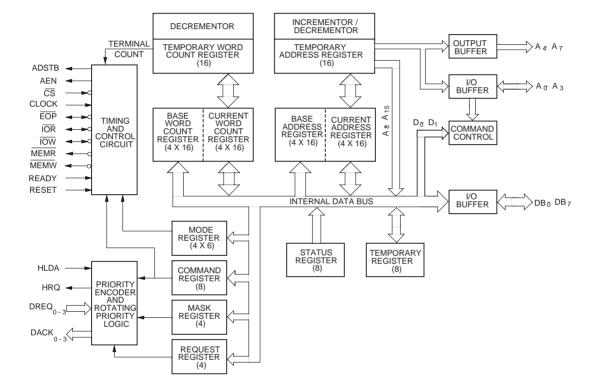

Figure 2-3: CA82C37A Block Diagram

## Table 2-1: Pin Descriptions

| Cumhal              | Pi                | ns                | Turne | News and Exaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|---------------------|-------------------|-------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol              | PLCC              | PDIP              | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

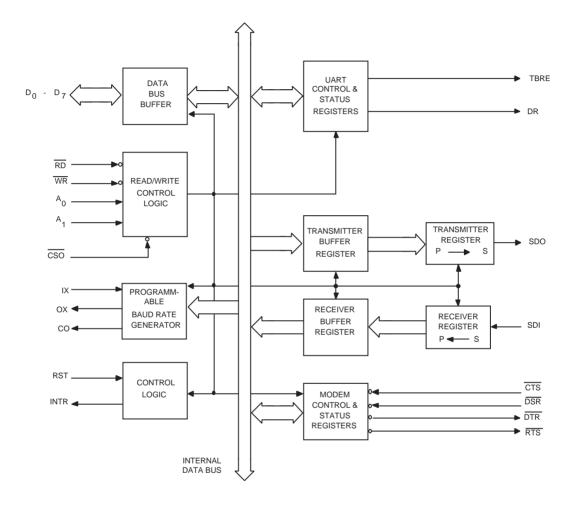

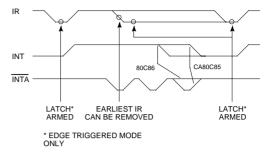

| A <sub>0-3</sub>    | 36-39             | 32-35             | I/O   | <b>Low Address Bus</b> : Bi-directional, 3-state signals. The 4 least significant address lines. Idle Cycle (Inputs). Addresses the CA82C37A control register to be loaded or read. Active Cycle (Outputs). Lower 4 bits of the transfer address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |